# Methodologies for Accelerated Open-Source Hardware Verification and Optimization

Farzam Gilani

A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

University of Washington

2025

Reading Committee:

Michael Taylor, Chair Mark Oskin Richard Shi Mehran Mesbahi

Program Authorized to Offer Degree:

Department of Electrical and Computer Engineering

## ©Copyright 2025 Farzam Gilani

#### University of Washington

#### Abstract

Methodologies for Accelerated Open-Source Hardware Verification and Optimization

#### Farzam Gilani

$\label{eq:Chair of the Supervisory Committee:} Michael Taylor \\$  Department of Electrical and Computer Engineering

The rise in development of open-source hardware and the demand for energy-efficient, highperformance computing have led to increasingly complex processor and accelerator designs.

While open-source tools streamline the design process, verification remains challenging and

costly, as it requires extensive testing to avoid costly post-silicon faults. Conventional formal

verification methods are limited by scalability, slow software simulators are slow, and FPGA

prototyping offer limited design visibility. To address these challenges, Condominium is introduced to couple the speed of FPGA emulation with the transparency of RTL simulation. By

enabling non-intrusive emulation and cycle-accurate data collection, Condominium provides

real-time instruction-level bug localization and fine-grained performance profiling, enabling

agile system evaluation methods for hardware engineers. Additionally, Condominium facilitates the precise emulation of peripherals and system calls, bypassing the need for extensive

RTL development. Furthermore, this dissertation introduces a novel high-fidelity hardware

coverage metric for elevating the efficacy of modern coverage-guided hardware fuzzers. By providing an accurate representation of design exploration By incorporating the relative latency information of the cascaded coverpoints into the metric, this high-fidelity metric aims to provide an accurate representation of design exploration to coverage-guided fuzzers. Through specially designed coverage engines integrated into Condominium, this work enables FPGA acceleration of high-fidelity coverage, addressing the scalability and acceleration issues of previously proposed coverage-guided fuzzers. By providing an environment for accelerated and cycle-accurate hardware emulation and the fine-grained verification methodologies it enables, this dissertation aims to provide a framework that addresses common challenges in hardware verification and analysis and significantly reduces engineering time spent on design functional verification and performance optimization.

# Contents

| $\mathbf{C}$ | onter | its                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                            | :  |  |  |

|--------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|----|--|--|

| Li           | st of | f Figures         iii           f Tables         iv           roduction         1           ckground         4           Challenges in Verification and Optimization of Hardware Designs         4           2.1.1 Hardware Simulation         4           2.1.2 Hardware Functional Verification         5           2.1.3 Hardware Performance Optimization         6           BlackParrot         7           2.2.1 BlackParrot Architecture         7           2.2.2 BlackParrot's Bring-up Evolution         10           ndominium         12           Acknowledgment         12           Motivation         12           Condominium Architecture         15           3.3.1 Zynq-based Architecture         16           3.3.2 Cycle-Accurate Emulation Layer         17           3.3.3 Heterogeneous Prototyping Cluster         20 | et of Figures                                              |    |  |  |

| Li           | st of | Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $\mathbf{s}$                                               | iv |  |  |

| 1            | Intr  | oducti                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ion                                                        | 1  |  |  |

| <b>2</b>     | Bac   | kgroui                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $\mathbf{nd}$                                              | 4  |  |  |

|              | 2.1   | Challe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | enges in Verification and Optimization of Hardware Designs | 4  |  |  |

|              |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | •                                                          | 4  |  |  |

|              |       | 2.1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                            |    |  |  |

|              |       | 2.1.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                            |    |  |  |

|              | 2.2   | Blackl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | •                                                          | 7  |  |  |

|              |       | 2.2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                            | 7  |  |  |

|              |       | 2.2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | BlackParrot's Bring-up Evolution                           | 10 |  |  |

| 3            | Cor   | ndomir                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | nium                                                       | 12 |  |  |

| •            |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                            |    |  |  |

|              | 3.2   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                            |    |  |  |

|              | 3.3   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                            |    |  |  |

|              | 0.0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                            |    |  |  |

|              |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | v · ·                                                      |    |  |  |

|              |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ·                                                          |    |  |  |

|              | 3.4   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | · · · ·                                                    |    |  |  |

|              | 9.2   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <u> </u>                                                   |    |  |  |

|              |       | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                            |    |  |  |

|              |       | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | · ·                                                        |    |  |  |

|              |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | v -                                                        |    |  |  |

|              | 3.5   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                            |    |  |  |

|              | 0.0   | 3.5.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Gate-Level Accelerated Emulation                           | 33 |  |  |

|              |       | 3.5.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Emulating Large Systems with FPGAs                         | 34 |  |  |

|              |       | 3.5.3   | Decomposed FPGA emulation              | 34 |

|--------------|-------|---------|----------------------------------------|----|

|              |       | 3.5.4   | FPGA-Accelerated Performance Analysis  | 35 |

| 4            | Higl  | h-Fidel | lity Coverage                          | 36 |

|              | 4.1   | Ackno   | wledgment                              | 36 |

|              | 4.2   | Motiva  | ation                                  | 36 |

|              | 4.3   | Backgr  | round                                  | 40 |

|              |       | 4.3.1   | Coverage Guided Fuzzing                | 40 |

|              |       | 4.3.2   | Contemporary Coverage Metrics          | 42 |

|              | 4.4   | High-F  | Fidelity Coverage                      | 44 |

|              |       | 4.4.1   | Latency-Aligned Group-Coverage         | 44 |

|              |       | 4.4.2   | Automated Coverage Instrumentation     | 46 |

|              | 4.5   | Accele  | rated Coverage Collection              | 49 |

|              |       | 4.5.1   | CAM-based Group Coverage Engine (CCE)  | 49 |

|              |       | 4.5.2   | Condominium Integration                | 51 |

|              | 4.6   | Evalua  | ation                                  | 52 |

|              |       | 4.6.1   | FPGA Implementation                    | 52 |

|              |       | 4.6.2   | Case Study: BlackParrot Pipeline       | 55 |

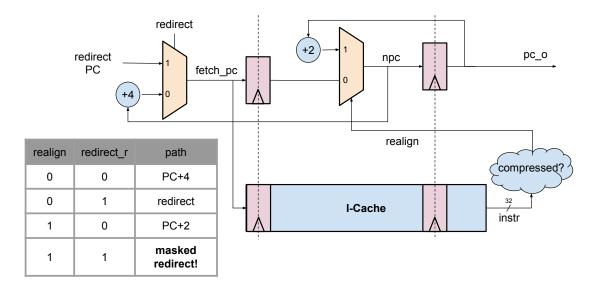

|              |       | 4.6.3   | Case Study: BlackParrot PC-Generator   | 57 |

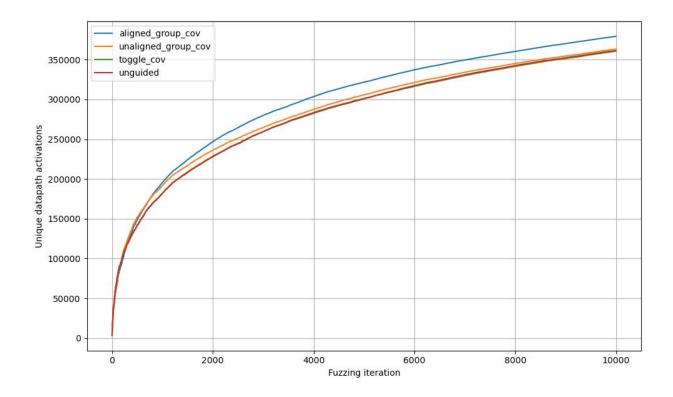

|              |       | 4.6.4   | Fuzzing Experiment                     | 59 |

|              | 4.7   | Relate  | d Work                                 | 61 |

|              |       | 4.7.1   | FPGA Acceleration of Coverage          | 63 |

|              |       | 4.7.2   | Coverage Metrics enabling Verification | 64 |

|              |       | 4.7.3   | Coverage-guided Fuzzing                | 64 |

|              |       | 4.7.4   | Fuzzing Hardware like Software         | 65 |

|              |       | 4.7.5   | Black-box Fuzzing                      | 65 |

|              |       | 4.7.6   | Targeted Coverage Verification         | 65 |

|              |       | 4.7.7   | Bug Injection and Fuzzer Evaluation    | 66 |

|              | 4.8   | Discus  | sion and Future Work                   | 66 |

|              |       | 4.8.1   | Evaluation of Latency-Aligned Coverage | 66 |

|              |       | 4.8.2   | One-to-One Coverage Mapping            | 67 |

|              |       | 4.8.3   | Progressive Coverage                   | 67 |

|              |       | 4.8.4   | BRAM-based Alternative to CCEs         | 67 |

|              |       | 4.8.5   | Extending to other Cores and HDLs      | 68 |

| 5            | Con   | clusion | n                                      | 69 |

| Bi           | bliog | raphy   |                                        | 72 |

| $\mathbf{A}$ | Sou   | rce-Co  | ode Repositories                       | 85 |

# List of Figures

| 2.1  | BlackParrot Sou Tiles                               | ð |

|------|-----------------------------------------------------|---|

| 3.1  | Condominium Shell Interface                         | 7 |

| 3.2  | Condominium AXI Abstraction                         | 8 |

| 3.3  | Condominium Clock-Gating                            | 0 |

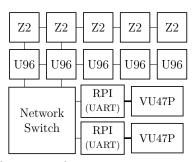

| 3.4  | Condominium Prototyping Cluster                     | 2 |

| 3.5  | Parallel ISA Cosimulation                           | 4 |

| 3.6  | Oracle Performance Profiler                         | 6 |

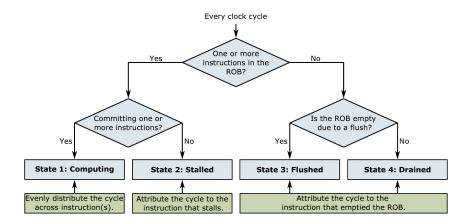

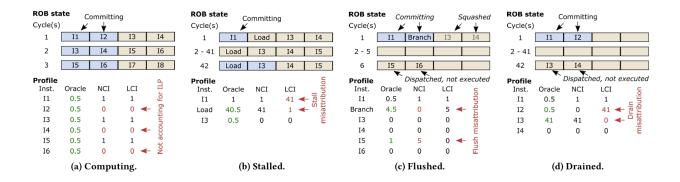

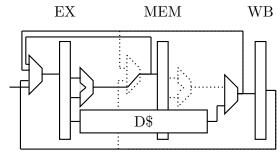

| 3.7  | Oracle Cycle-Attribution                            | 6 |

| 3.8  | Condominium Performance Profiling Slowdown          | 7 |

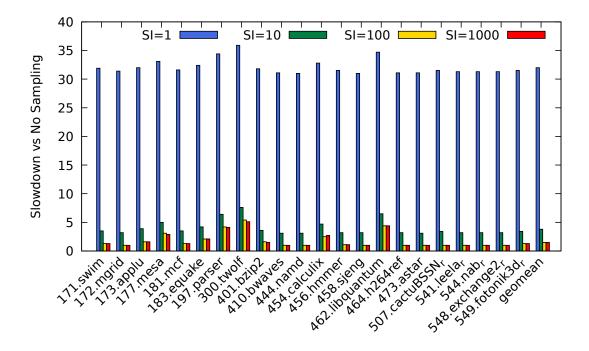

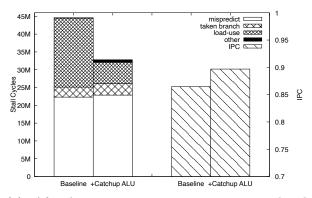

| 3.9  | Condominium Performance Profiling Stall Breakdown   | 8 |

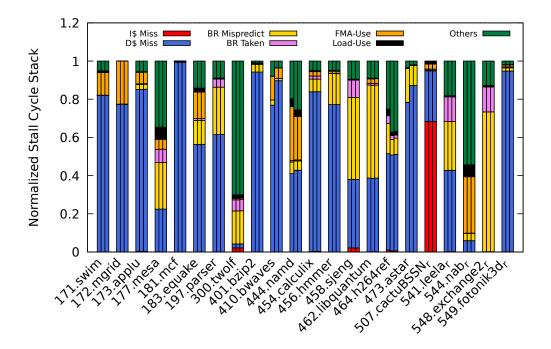

| 3.10 | Condominium Performance Profiling Attribution Error | 0 |

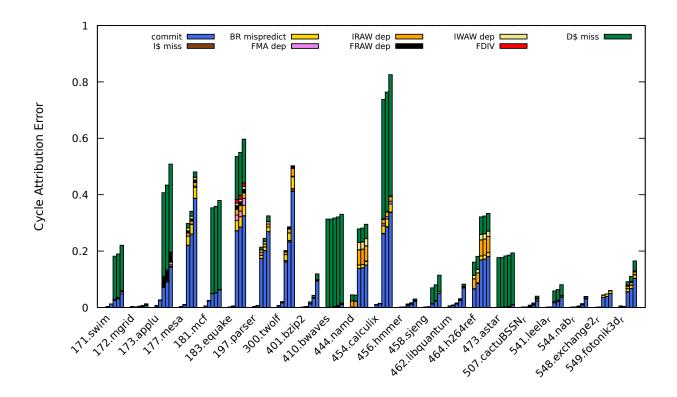

| 3.11 | Catch-up ALU Case Study                             | 1 |

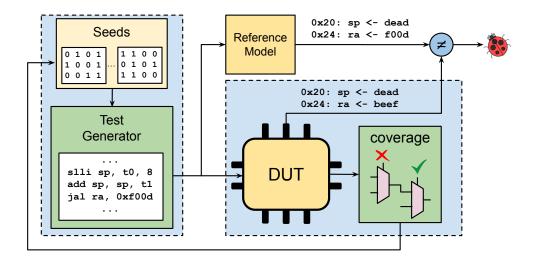

| 4.1  | Coverage-guided Hardware Fuzzing Loop               | 0 |

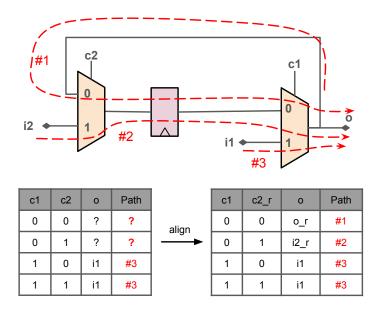

| 4.2  | Coverage Latency Alignment Example                  | 5 |

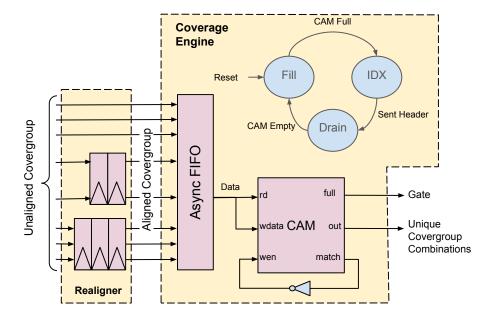

| 4.3  | CAM-based Group Coverage Engine                     | 0 |

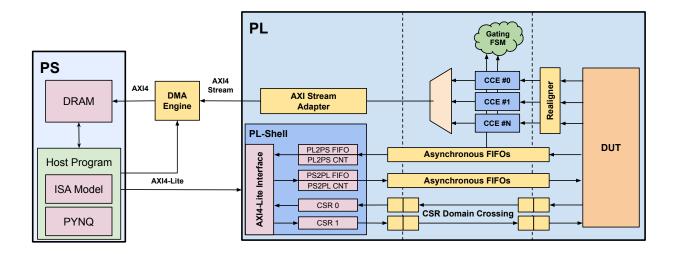

| 4.4  | CCE Condominium Integration                         | 1 |

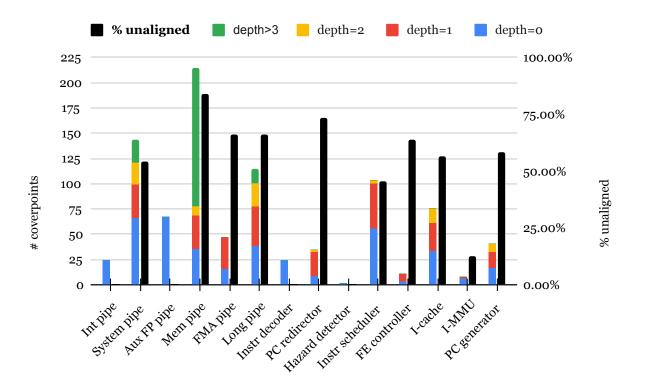

| 4.5  | BlackParrot Covergroup Breakdown                    | 3 |

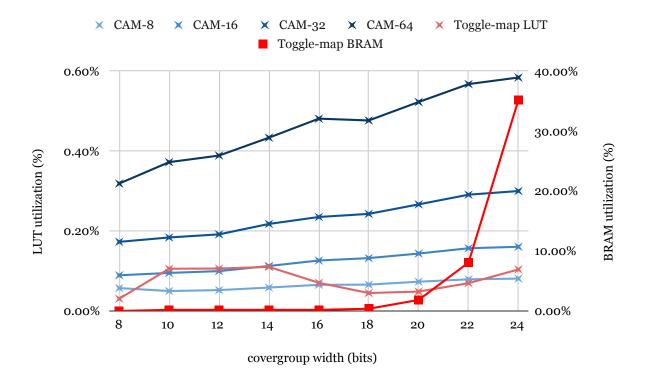

| 4.6  | CCE Utilization Comparison                          | 4 |

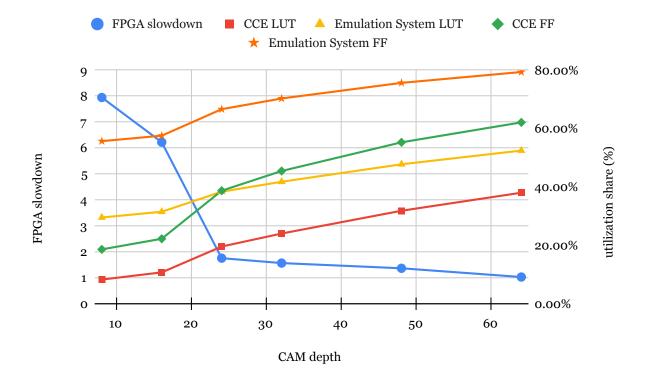

| 4.7  | CCE Depth vs Slowdown Tradeoff                      | 5 |

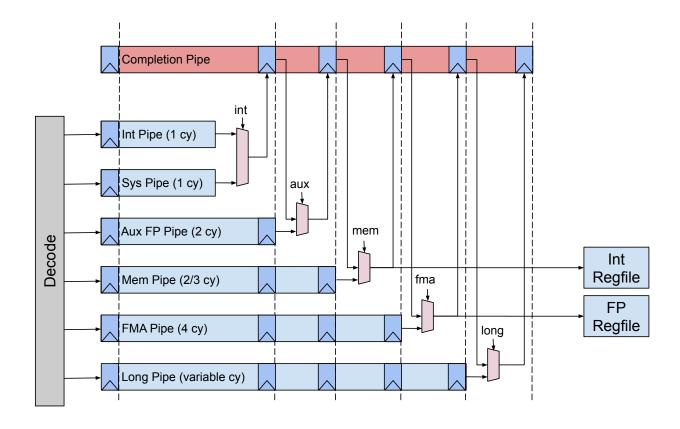

| 4.8  | BlackParrot Pipeline Case Study                     | 7 |

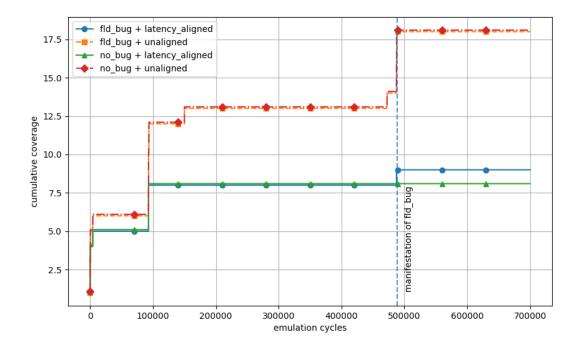

| 4.9  | BlackParrot FLD Bug Manifestation                   | 8 |

| 4.10 | BlackParrot PC-Generator Case Study                 | 9 |

| 4.11 | Coverage-guided Fuzzing Experiment                  | 2 |

## List of Tables

| 3.1<br>3.2<br>3.3 | POSIX System-Call Categorization                 | 33<br>34       |

|-------------------|--------------------------------------------------|----------------|

| 4.1<br>4.2<br>4.3 | High-Fidelity Coverage through Latency Alignment | 46<br>49<br>63 |

| ${f L}$ i         | ist of Algorithms                                |                |

| 1 2               | Coverage Instrumentation Algorithm               | 48<br>61       |

### Acknowledgments

The PhD program is a journey of constant learning and facing challenges and I am grateful for experiencing it at Bespoke Silicon group alongside a group of excellent engineers and researchers. First and foremost, I owe my sincerest thanks to my advisor, Prof. Michael Taylor, whose mentorship, insightful feedback, and positive enthusiasm fueled my work throughout this journey. Many of the projects I participated in during the program seemed insurmountable, but Michael's guiding insights always proved valuable. I want to also thank Prof. Mark Oskin and Prof. Ajay Joshi whose collaboration on the BlackParrot project provided a unique learning experience during the first years of my PhD.

I was also fortunate to work alongside and learn from many talented students at University of Washington. I want to thank Scott Davidson, Paul Gao, Huwan Peng, Tommy Jung, Mark Wyse, and Yuan-Mao Chueh for their insights and the great learning opportunity they provided me during our collaboration on BlackParrot and other projects. I want to specially thank Daniel Petrisko and Anoop Mysore Nataraja for their indispensable collaboration on the work on Condominium and High-Fidelity Coverage, which would have been not possible without their critical contributions.

I started my PhD journey with as an international student migrant and I want to acknowledge the support I received from friends that made facing the challenges of this transition possible. I want to thank Farzam Ebrahimnejad, Keivan Alizadeh, Artin Tajdini, and Diego Peña-Colaiocco for their support and friendship. I would also like to remember my late friend Ali Saffari whose fond memory will always stay with me.

I want to thank my parents, grandparents, and my brother Parham, and recognize their unconditional love and support throughout my life. They dedicated all they had so I can reach my goals and overcome life challenges, and I would not be here without their limitless support and sacrifice. While we have been separated for many years as I moved for my studies, they kept on supporting me from abroad. I look forward to finally reunite with them in the near future as I finish this chapter in my life.

In the end, I want to express my gratitude to my spouse, Mojdeh Kashani. I was extremely lucky to meet and marry someone who stood by my side and supported me during all of life's ups and downs. Mojdeh, thank you for always being there for me and having faith in me during times of hardship and uncertainty. I know building a life together during graduate studies has been challenging, but you always proved to be a pillar of unconditional love, encouragement, and stability in our lives. I had the privilege of receiving critical support from you and your family during the final years of my PhD journey which I will always appreciate. Mojdeh, thank you for believing in me, I would have never reached where I am today without you, and for this, I love you and thank you from the bottom of heart.

## Chapter 1

## Introduction

The emergence of open-source hardware, alongside the growing need for more energy-efficient and high-performance computers, has resulted in an explosion of increasingly complex processor and accelerator designs. As open-source tools and hardware libraries [131, 142] continue to streamline the design process to cater to more agile chip-design practices, verification of complex designs has remained a costly and time-consuming exercise [50]. Extensive verification is specially important in hardware development because as opposed to the software domain, post-release patches are not possible and post-silicon faults can be very expensive to find and resolve. While formal verification methods can be helpful, they're not scalable and a big portion of verification effort is spent on dynamic testing. However, the slow nature of software RTL simulators and the black-box nature of FPGA prototyping complicates design verification in the intermediate stages of design development. This problem is compounded by, in many domains, lack of well established software for custom designs which forces hardware designers to also design software in parallel which can be prone to bugs, extending the verification issue to another domain. Furthermore, as opposed to software development, lack of plug-and-play IDE environments with easy-to-use interfaces and bug localization further complicates hardware evaluation. In this dissertation, we inspect the challenges facing common techniques in design analysis and propose methodologies for bypassing the limitations on underlying experimental environment and streamline the overall development process.

Condominium is designed to address these challenges in hardware verification and optimization by providing an environment that joins the accelerated emulation speed of FPGAs with the design transparency of software RTL simulation. Condominium is implemented in a Zynq environment where design is emulated on a programmable logic and controlled by the Zynq processing system that handles tasks like DUT initialization, configuration, and collection of cycle-accurate microarchitectural information from DUT which can be used for debugging, performance profiling, and other experiments. Condominium aims to achieves the latter goal in a way that's non-intrusive to the DUT emulation to enable reproducibility and migration between FPGA and simulators by employing a clock-gating mechanism

that can pause DUT emulation when backpressure is needed for processing streamed microarchitectural data. Condominium enables us to significantly accelerate the process of improving hardware designs, in this case BlackParrot, and establish efficient mechanisms for ensuring functionality and performance of BlackParrot throughout its development cycle. To ensure ISA compatibility, perform accelerated functional verification, and automate bug localization, we leverage Condominium to gather run-time instruction execution information and perform ISA cosimulation by cross-comparison of the execution stream with an ISA model hosted in the host. To enable accelerated and detailed performance analysis of design over complex and long-running real-life benchmarks, we leverage Condominium to gather cycle-accurate instruction and stall source cycle attribution of processor during benchmark execution. This information enables us to identify exactly how many cycles each instruction is contributing to overall execution and provide stall type categorization for each cycle. Finally, we use Condominium to emulate the timing and functionality of various peripherals and system-calls that can be employed in conjunction with the DUT without the need to explicitly implement them in RTL.

While relying on established benchmarks for testing helps designers moderately explore the design space triggered by those benchmarks, they are not extensive and heavily rely on programming patterns choices employed by software programmers. To further evaluate the design, researchers have opted for various shades of random testing. Coverage-guided Fuzzing is a method that aims to steer a random test generator during an iterative process to maximize the overall achieved design coverage, and by proxy, maximize the newly explored design states. However, as algorithms for coverage-guided fuzzing mature and become better at exploring the design space, they cannot fully flourish their verification potential due to poorly designed coverage metrics that guide these fuzzers. Contemporary coverage metrics often do not provide a representative feedback on the degree of design exploration and are also difficult to prototype for FPGA accelerated fuzzing. In this dissertation, we introduce a high-fidelity coverage metric that aims to provide an accurate feedback for modern fuzzers. By incorporating relative RTL latency information into covergroups, high-fidelity coverage disambiguates previous metrics by establish a deterministic mapping from coverage values to activated RTL datapaths. Furthermore, by introducing specialized coverage engines, that integrate into the Condominium infrastructure, this work enables FPGA acceleration of group-coverage guided fuzzing. Finally, we inspect the efficacy of proposed high-fidelity coverage by evaluating slowdown-utilization tradeoffs on FPGAs, presenting case studies on bugs uniquely identified by the metric, and performing comparative fuzzing experiments using other metrics.

Portions of this work were partially supported by Air Force Research Laboratory (AFRL) and Defense Advanced Research Projects Agency (DARPA) under agreement numbers FA8650-18-2-7863 and FA8650-18-2-7856; NSF grants SaTC-1563767, SaTC-1565446. This work intersects and leverages research and infrastructure created by the members of the Bespoke Silicon Group, spanning across accelerators ([12, 20, 24, 31, 54, 63, 64, 65, 94, 109, 111, 112,

113, 114, 126, 127, 133, 162, 163, 171, 183, 185]), ML ([161]), ASIC Clouds ([95, 96, 103, 140, 143, 151, 153, 172]), open source hardware ([48, 142, 152]) RISC-V ([2, 42, 44, 85, 87, 101, 107, 115, 120, 121, 124, 125, 160, 184]), Network-on-Chips ([86, 97, 116, 147, 186]), security ([6, 19, 34, 35, 71, 72]), benchmark suites ([21, 98, 155]), dark silicon ([26, 63, 66, 138, 139, 144, 162]), multicore ([38, 39, 67, 68, 69, 97, 115, 137, 141, 145, 146, 147, 148, 149, 150, 164]), compiler tools ([1, 15, 56, 57, 58, 81, 82, 83, 84, 182]) and FPGAs ([21, 76, 187]).

## Chapter 2

## Background

## 2.1 Challenges in Verification and Optimization of Hardware Designs

The economic and engineering burdens imposed by modern computer-architecture projects now routinely exceed those of comparable software endeavors. Whereas software can be iterated, deployed, and patched at negligible marginal cost, hardware design demands large up-front non-recurring engineering (NRE) investments, extended verification cycles, and complex multidisciplinary coordination across RTL, physical, and manufacturing domains. Because this economic cliff exists, hardware teams front-load verification far more aggressively than software projects. Furthermore, unlike software, RTL describes thousands of state elements toggling concurrently, creating an exponential state-space that forces cycle-accurate simulators to run multiple orders of magnitude slower than real silicon, where even a one second of program time can consume a full day of wall-clock time. The result is a development process that is demonstrably more costly and time-consuming than software development. In this section we describe current methods in simulation, functional verification, and performance optimization of hardware projects and highlight the factors contributing to their long iteration times and complexity.

#### 2.1.1 Hardware Simulation

Cycle-accurate RTL simulation is the recurring element in hardware design process, and while users rely on it for design, verification, and optimization, it routinely becomes the bottleneck affecting the process. Running single-threaded RTL simulators, such as Verilator [131], can yield and emulated clock speed of 1 KHz - 1000 KHz on modern x86 hosts [47]. On the other hand, native software can be executed on the same host at multi-gigahertz speeds. The multiple orders of magnitude slowdown from software to hardware simulation lends itself to complex nature of simulating RTL designs on a non-native software environment. The main

source of this slowdown is due to the concurrent emulation of logical units on a sequential host. For every simulated RTL cycle, thousands of flip-flops and combinatorial computational units should be inspected and their output updated. To ensure the correct update order in the netlist, for every cycle the netlist graph of the RTL needs to be traversed and RTL units scheduled to be updated in the corresponding order. This has led to software RTL simulators to spend a dominant fraction of the cycle simulation time just for scheduling and ordering logic update events [23]. Furthermore, modern test-benches often include random test generation, data monitoring, waveform dumping, and DPI calls on every cycle that cross the HDL/C++ boundary and cost extra host execution cycles. While techniques like data reuse have been used to increase the performance of software RTL simulators by skipping inactive portions of hardware [110], the speedup is within one order of magnitude, and does not offer a solution for simulating real-life programs.

FPGA prototyping can be used as an alternative to accelerate RTL emulation, clocking designs at 10 MHz - 100 MHz for multiple orders of magnitude speedup over software RTL simulation. Suddenly, benchmarks that take days to simulate on software can be tested within minutes on FPGAs. This speedup, however, comes at the cost of full design visibility. This tradeoff can cause a significant hurdle when hardware design moves from early stages of reliance on software simulators to FPGA emulation. When designers move to FPGA emulation, the full design visibility that is crucial to quick debugging and evaluation becomes a challenge to be dealt with. Synthesized hardware probes [13] can be used to get a glimpse of a set of design signals, however this needs pre-planning and usually offer a limited visibility window as limited FPGA block-RAMs are used to store the data. The limited visibility forces users to decide on what set of signals to choose for monitoring and when to monitor them throughout emulation. The uncertainty cause by this limited visibility, in turn, may cost many extra iterations of trial-and-error if users lack the prior knowledge of what they are looking for, which is exacerbated by the long FPGA bitstream generation times, leading to hours of re-synthesis for locating an issue. When migrating from slow, but transparent software RTL simulators to fast, but hard to probe FPGA emulation, a framework must be developed for using FPGAs for design verification and optimization that bridges this gap in a way that designers can secure the acceleration without facing aforementioned challenges.

#### 2.1.2 Hardware Functional Verification

As chips grow in both complexity and application variety, functional verification has grown to be both a crucial and time-consuming part of the hardware development process. A survey studying the state of ASIC design and verification industry in 2024 [50] highlights staggering statistics on the impact of verification on ASIC project timelines. According to this survey, while design engineering teams are supposed to be focused on developing new IP, they spend on average 49% of their time on functional verification. Additionally verification engineering teams spend, on average, 47% of their time on just debugging as opposing to developing new testing schemes and designing test-benches. Even with the significant

man-hours invested into hardware verification, around 75% of ASIC projects report being behind schedule while only 14% of projects achieve first time silicon success. The significance of verification bottleneck, coupled with the multi-million dollar cost of re-manufacturing faulty chips highlights the need to development of agile and accurate functional verification techniques, specially in an open-source ecosystem, that can provide faster turnaround times for hardware verification.

Conventional methods of hardware verification include formal verification, unit testing, ISA compliance testing, benchmarking, and random constrained testing or fuzzing. Each of these methods can be effective in different stages of hardware development. For example, ISA compliance tests can ensure basic functional correctness in early stages, unit tests can be employed throughout the process for maintain individual logical units, and fuzzing can be used to catch unpredictable corner-case bugs as design matures and passes conventional benchmarks. Many of the aforementioned challenges facing software and FPGA emulation of the RTL also directly affect verification practices. As design verification moves away from hand-crafted short tests, software simulation suffers from long program runtime which is exacerbated when multiple re-runs are needed for discovering and resolving bugs. Due to delayed manifestation of bugs, localizing bug trigger points can be difficult even with the full transparency of software simulation. Moreover, the limited visibility window and signal bandwidth of FPGA emulation means they cannot easily be used for verification if user lacks prior knowledge on what signals to monitor and how to define a time point to capture the signal visibility window for debugging. Multiple FPGA synthesis reruns caused by misprediction of probed signals and trigger points for window capture in logic analyzers can cost days of idle time for verification engineers. Methods like ISA cosimulation [88, 89, 102, 154 are therefore needed to localize bug trigger points billions of cycles into programs, like Linux boot, saving verification engineers significant time in searching waveforms for sources of errors. Furthermore, since finding and fixing bugs usually includes running tests multiple times, methods like architectural checkpointing [16, 128] can be used to quickly reload simulation state to a snapshot of the design before the bug trigger point to test potential fixes. This checkpoint snapshot, in turn, can be used to move verification between FPGA and software simulation to leverage the transparency and speed tradeoff between the two environments. Finally, as engineers move towards fuzzing, verification challenges are compounded due to limited FPGA utilization and bandwidth for coverage collection and inaccurate coverage metrics misguiding the fuzzing algorithm and wasting testing iterations. This is specifically important because for an iterative verification process, a lower loop turnaround time and better guidance usually means higher design exploration and higher chance of revealing design bugs and vulnerabilities.

### 2.1.3 Hardware Performance Optimization

Hardware performance analysis usually is performed in conjunction with functional verification in later stages of development. Similarly, the same challenges with functional verification apply to performance optimization since both rely on extraction of microarchitectural information from RTL during benchmark execution. While custom designed tests alongside conventional benchmarks such as CoreMark [55], SPEC [32, 73, 74], and Linux kernel [156] can be used for stress testing different parts of hardware, simple metrics like instructions-perclock (IPC) do not provide any indicators on the RTL and program bottlenecks contributing to overall performance. Modern processors provide built-in event-driven performance counters, usually for debugging purposes, that can be used for gaining better optimization insight [104], however, these counters are hardened to count predetermined events do not provide information on the extent that these events contribute to performance bottlenecks [166]. To obtain a fine-grained data on sources of performance bottlenecks, engineers have proposed sophisticated performance profilers that attribute each execution cycle to the corresponding offending instruction and logical stall sources [61, 62]. However, the use of these performance profilers has proven challenging in conjunction with FPGAs due the bandwidth required for streaming and processing the per-cycle attribution information. Solutions like software interrupt based performance sampling have been offered to mitigate the bandwidth issue, but they are prone to misattribution sampling errors and also perturb the normal benchmark flow during interrupt handling which can influence performance analysis. These challenges highlight the need for developing performance profiling techniques that provide fine-grained and cycle-accurate performance information without introducing sampling errors and perturbing the benchmark's execution flow.

### 2.2 BlackParrot

Much of the work in this dissertation was motivated by the need for development of agile functional verification and performance analysis methods during development of the Black-Parrot RISC-V processor. In this section, we briefly introduce BlackParrot and go though the challenges that prompted the work on said methods.

#### 2.2.1 BlackParrot Architecture

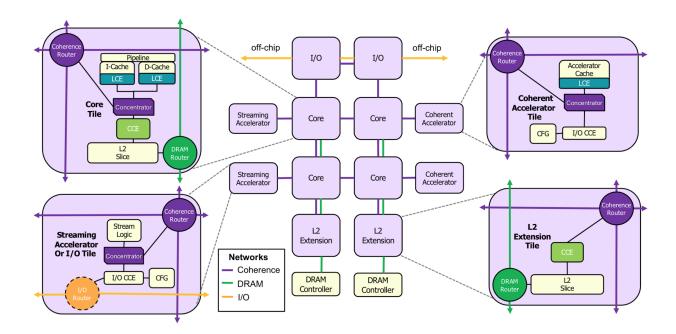

BlackParrot [115] is a RV64GC processor designed at Bespoke Silicon Group that aims to become the default open-source Linux-capable RISC-V multicore used by the world. It's designed as a modular and highly configurable core with well defined and latency-insensitive interfaces that enable users to easily modify various components to be tuned for their application. Use cases range from a unicore serving as a host accelerator controller, to a multicore capable of executing complex programs, like Linux, with great performance. BlackParrot also provides more configurability by ensuring race-free programmable cache coherence through distributed directory-based coherence engines [170] that enable users to implement various coherence protocols, such as MESI, through micro-programming. BlackParrot is designed as a scalable, heterogeneously tiled SoC composed of different tiles designed for compute, L2 extension, and IO and accelerator tiles interfacing with the SoC network (shown in Fig-

Figure 2.1: BlackParrot multi-core SoC comprise a mesh of heterogeneous tiles, allowing flexible composition of cores, accelerators, L2 cache slices, I/O, and DRAM controllers. Core tiles implement a processor, a cache coherence engine, and an L2 slice. Coherent accelerator tiles implement an accelerator that has access to the cache coherent memory system. L2 extension tiles allow the amount of L2 cache to be changed. Streaming accelerator or I/O tiles allow flexible interfacing of a common memory system via a shared non L1-cached address space that is routed over the coherence network.

ure 2.1). The BlackParrot core complex is functionally partitioned into three main sections, Front End, Back End, and Memory End, each fulfilling their specific purpose and communicating with each other through well defined interfaces.

#### BlackParrot Front End

The Front End (FE) is responsible for speculatively fetching instructions from the memory and providing the execution pipelines with stream of speculative PC-instruction pairs. To this end, FE consists of 2 major components: pc-generation and the instruction cache. The PC generation module provides speculative PCs to the instruction cache. It contains a Branch History Table (BHT), a Branch Target Buffer (BTB) and a Return Address Stack (RAS). The BHT and BTB together provide the next PC prediction on branching instructions. When the 2-cycle instruction cache returns the fetched instruction, it is partially decoded to determine whether it is a conditional branch, function call, or function return. This

information is used in conjunction with the branch buffers and RAS to determine whether to use the currently predicted next PC or to override with a target calculated from the decoded instruction. The instruction cache is a Virtually-Indexed Physically-Tagged (VIPT) cache with two pipeline stages: Tag Lookup (TL) and Tag Verify (TV). There are 3 hardened memories in the instruction cache, the data, tag and stat memories which are implemented as single-port read-write synchronous RAMs to be amenable to most commercial SRAM generators. In TL, the data memory and tag memory are accessed. In TV, the data from these caches is selected based on the result of the tag comparison. A small stat mem contains the line access and replacement information for each set and is updated in TV as well. The instruction cache is non-stalling, requiring a replay on missed instructions. To enable virtual address translation, an instruction Translation Lookaside Buffer (TLB) is included as a small fully-associative buffer with a single-cycle access time. It is accessed in parallel with instruction cache and provides it with the translation physical tag for comparison. Note that the Front End does not independently modify the processor's architectural state and is logically controlled by the Back End through PC redirections caused by non-speculative resolution of branch mispredictions or trap handling.

#### BlackParrot Back End

The Back End (BE) is responsible for the non-speculative execution of RISC-V instructions. It receives a speculative instruction stream from the FE and processes them in order. To simplify physical design and reduce complexity for verification, the BE consists of a single stall point and a single commit point in the execution pipelines. The BE consists of multiple sections managing instruction execution and architectural state. The calculator unit hosts an array of non-stalling execution pipelines with varying latencies, each handling a subset of RISC-V instruction types. These include a 1-cycle integer pipe for handling simple ALU operations, a 1-cycle system pipe for handling CSR instructions, a 2/3-cycle memory pipe for handling memory operations include SV39 page-table handling, a 2-cycle auxiliary floating pipe for handling type conversions, a 4/5-cycle floating pipe for handling arithmetic operations, and a dynamic-latency pipe for handling long floating-point division and root operations. Furthermore, a hazard detector unit hosts logic for identifying data, structural, and control hazards within pipeline instructions, and stalling the pipeline when a dependency cannot be bypassed through data-forwarding. A director unit observers branch misprediction, traps, and other synchronization events and issues PC redirections to the FE to redirect the instruction fetch. Finally, a scheduler unit is tasked with receiving PC-instruction pairs from the FE, decoding them, reading register files, and dispatching them to execution pipes.

#### BlackParrot Memory End

The BlackParrot Memory End (ME) implements the Bedrock [170] protocol for providing cache coherence between processor cores, coherent accelerators, and the memory system. The Bedrock system consists of a coherence network, local cache engines (LCE), and cache

coherence engines (CCE). The LCEs are cache controllers that manage coherence transactions for a single instruction or data L1 cache. The LCE interfaces on one side with the L1 cache and on the other side with the Bedrock coherence network. The LCE ensures coherence for its corresponding cache by issuing requests on a cache miss and responding to coherence update commands received from the network. The CCEs are coherence directories responsible for maintain coherence for independent subsets of memory address space. The CCE operate as programmable microcode engines executing both RISC-style general purpose operations and more complex coherence-specialized operations aimed at accelerating common cache coherence operations with most instructions executing in a single cycle. The engine is consists of a fetch stage for instruction decoding, branch prediction, and preforming redirections and an execute stage for handling all instruction execution and branch resolution. The CCE contains 8 64-bit general purpose registers, a miss status handling register to track the status of the current outstanding request, and coherence network ports for sending and receiving messages on the Bedrock network. The CCE also contains dedicated coherence directory storage, speculative memory access tracking storage, and pending bit storage.

### 2.2.2 BlackParrot's Bring-up Evolution

Maintaining a heterogeneous SoC such as BlackParrot with a high degree of configurability needs a robust framework for continuous verification and performance analysis so designers can quickly identify bugs and performance bottlenecks as the design matures throughout its development process. These verification methods can be integrated into the project's continuous integration (CI) [49] routines to ensure continuous design correctness with every major change in order to avoid back-tracking months into development when we face a bug. The first tier of testing used for early verification of BlackParrot has been the usage of simple ISA compliance benchmarks using RTL simulation alongside unit testing the various functional blocks of BlackParrot to ensure their functional correctness in isolation. The latter is specially effective because of the use of latency-insensitive interfaces between BlackParrot's functional units enables independent verification of various functional units without maintaining assumptions about handshake constraints with other units. However, as BlackParrot matured, the need arose for better testing methods that can handle longer and complex benchmarks and can deliver the performance and design transparency needed for more extensive verification.

The Linux kernel serves as a stepping stone benchmark for functional verification and continuous maintenance of RISC-V cores as it utilizes almost every feature in the RV64G ISA. However, moving from simple ISA compliance tests to Linux for the purposes of BlackParrot verification turned out to be non-trivial and prompted a rethinking of our early verification infrastructure. First, a mechanism was needed to reliably find program diversions from the ISA specification. This was motivated by the fact that building a working Linux environment for an early-stage processor needed the exact cooperation of many building blocks, including a custom firmware [167] to handle BlackParrot-specific bare-metal responses to

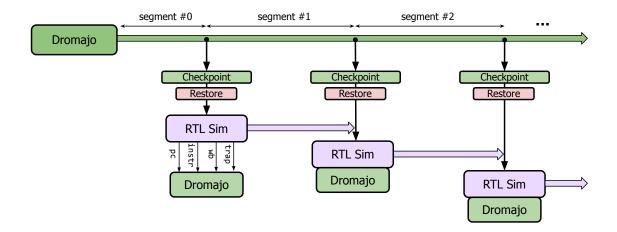

kernel system-calls, so there was a need to reliably distinguish program crashes due to a faulty kernel from bugs related to fault hardware as they should be dealt with completely differently. Second, since the Linux kernel is a complex program involving long-running tasks and context switches, an RTL bug could be triggered in a certain cycle but not manifest until millions of cycles after, or maybe not at all. Finally, software debugger tools, like GDB [59], hosted on the hardware are prone to the same bugs they are tasked to identify and therefore unreliable. In order to avoid wasting verification cycles on manually resolving above challenges, we employed an ISA cosimulation method to simulate BlackParrot in lockstep with a golden RISC-V reference model [88] to instantly identify RTL divergence from acceptable ISA behavior by cross-comparing instruction execution metadata with the reference model. Furthermore, as an intermediate method to cut-down the total co-simulation time, we leverage architectural state checkpointing [88, 102] in ISA simulators to break down program execution into several segments and perform ISA cosimulation for each segment independently and in parallel on different server threads.

While parallelizing software-based ISA cosimulation provided an opportunity to integrate maintenance of long benchmarks into the BlackParrot CI pipeline, achieving an interactable and real-time experience of Linux boot motivated the migration of this verification technique to the FPGA domain. What followed was development of a Zyng-based FPGA infrastructure that enabled acceleration of BlackParrot emulation while maintaining the ability to extract cycle-accurate execution data streams from the RTL without perturbing the design. Similarly, as the need for performance analysis and optimization of BlackParrot promoted the use of industry-standard benchmarks such as SPEC [32, 73, 74], and more fined-grained performance profilers were leveraged to provide us with a cycle-accurate breakdown of Black-Parrot's performance bottlenecks, we employed the same Zyng-based FPGA infrastructure to perform the duty. Moreover, the same infrastructure proved to be useful in cycle-accurate timing modeling of BlackParrot peripheral, like DRAM, and Linux system-calls executed by proxy on an x86 host controller. In chapter 3, we introduce this FPGA emulation infrastructure and how it aids users in agile design analysis. Finally, we explored using coverage-guided hardware fuzzing for better random verification and catching corner-case bugs potentially missed by conventional benchmarks. As we made improvements to the current approaches and developed a high-fidelity coverage metric for better guidance of fuzzing loop, we employed the same FPGA infrastructure to enable high-throughput streaming of coverage data which was needed but overlooked in previously introduce fuzzing methodologies. In chapter 4, we introduce this high-fidelity coverage metric and how it can be effectively employed for better hardware fuzzing.

## Chapter 3

## Condominium

## 3.1 Acknowledgment

Research in computer architecture is an intensive collaborative effort, and the work on Condominium has relied very heavily on contributions from fellow BSG members: Dan Petrisko, Anoop Mysore Nataraja, Zoe Taylor, and Prof. Michael Taylor. I would like to thank Prof. Taylor and Zoe Taylor for the physical design and assembly of the Condominium cluster, Dan Petrisko for the design of the PS-PL interfaces and the Scale-down conceptualization, and Anoop Mysore Nataraja for the design of the clock-gating mechanism.

### 3.2 Motivation

The ever-increasing complexity of processors and the explosion of domain-specific accelerators motivated by the end of Dennard Scaling [28] have amplified the importance and the cost of fine-grained design analysis and verification. Hardware designers are faced with a diverse plethora of processors and accelerators, each presenting unique verification challenges both in terms of functional correctness and performance evaluation that, as opposed to software design, need to be carefully analyzed and ironed out before tapeout. Early in the hardware development process, architects can leverage the transparency of RTL waveform inspection to identify hardware units contributing to performance bottlenecks and functional vulnerabilities and quickly offer and verify fixes. However, cycle-accurate software RTL simulations are painfully slow, so as the design matures throughout its development process, the need for longer testing with real-life benchmarks renders relying on RTL simulation for verification unsustainable. Moreover, when analyzing target program performance on silicon, software engineers use simple performance counters which are decided on and built-in early in the hardware design. These performance counters are sampled and aggregated to be leveraged by software performance tools, like perf [165], to gain performance insight for a target program. On the other hand, when aiming to optimize a target hardware for conventional software benchmarks, hardware engineers need to gain cycle-accurate insights about various hardware units contributing to performance bottlenecks. This requires design of sophisticated RTL performance profilers that tightly couple with the design and replicate its events effecting software execution pipelines. Using these RTL profilers, hardware engineers can model how an instruction creates a bottleneck in a specific design unit and measure how many cycles it costs the overall benchmark execution. Similarly, this needs an accelerated hardware emulation approach that can maintain the ability to extract a high-throughput stream of profiler data for performance analysis.

Traditionally, architects have approached this dichotomy by performing early prototyping in FPGA. By doing so, RTL very similar to tapeout designs can be emulated with cycle accuracy at  $10^2$ - $10^4$ x [92] faster than simulation alone. For hardware designers to experience a smooth migration of verification methodologies from software RTL simulation to FPGA emulation, the underlying environment should provide a comparable level of cycle-accurate insight into the design. Furthermore, for purposes of conducting realistic performance analysis, the FPGA environment should be able to provide standardized guaranties on the behavior and timing of various IO peripherals interacting with the design. This ensures that the many tools and techniques developed for functional verification and performance evaluation in the early stages of the hardware development process can be ported into the new environment and continue to maintain the design quality with the same level of rigorous inspection. However, prototyping large hardware systems can often be challenging due to the limited available resources on conventional development boards. Large companies can Scale-Up their prototyping systems using large commercial emulation platforms [33, 105, 134], but these are usually unaffordable to academics and startups. Others have proposed Scale-Out solutions that leverage cloud FPGA clusters [3, 8] to emulate large SoCs as a more affordable option than scale-up solutions. However, his approach generally relies on regularity in the design. Furthermore, cloud clusters usually limits engineers to using certain standardized interface and memory systems such as PCIe [130] that offer higher access latencies, multiple microseconds, and further latency jitters due to network packets being transporter over Ethernet controllers and host software packet routing [92]. This is specially important if the design emulation relies on ensuring low-latency access to DRAM and other peripherals and can cause further slowdowns in real emulation speed. Also, since cloud FPGAs use hourly pricing [7], the scale-out solutions relying on them can become non-affordable for long-term design maintenance and continuous integration.

To provide an environment that addresses the mentioned challenges, we propose Condominium, a Scale-Down approach for architectural prototyping. Instead of unilaterally scaling up a chip design from an FPGA prototype to a full tapeout, it is more economical for academics to scale-down the design to prototype design subsystems for rigorous verification and reserve the scale-out approach for full system prototyping during tapeout events. Using local FPGA boards for scale-down prototyping of design subsystems can give deep debugging insights into effects of incremental design modifications and accelerate the design

Table 3.1: On a per-FPGA basis scale-down systems require a much smaller investment, allowing teams to incrementally build up their verification infrastructure using heterogeneous boards for a variety of target subsystems. The Ultra96v2 board cost breaks even after 4-months of smallest AWS-F1 instance usage.

| Strategy                | $year/FPGA^0$ | Logic Unit  | Required I/O |

|-------------------------|---------------|-------------|--------------|

| Scale-Up <sup>1</sup>   | ~\$6700       | Full Design | Native PCIe  |

| $Scale-Out^2$           | $\sim $900$   | Tile        | PCIe Tunnel  |

| Scale-Down <sup>3</sup> | $\sim$ \$100  | IP Block    | SSH/Serial   |

<sup>&</sup>lt;sup>0</sup> 2000 hours is equivalent to a year of 8-hour regressions.

verification process in a more economical way that the state of-the-art alternatives. Because iteration time is much faster than monolithic prototypes, small design teams can quickly bootstrap new subsystems, run long simulations, ensure functional correctness, analyze performance consequences, and quickly iterate on potential fixes. Previous FPGA emulation platforms [33, 41, 92, 134] are expensive, dependent on vendor IP, or cumbersome and prone to lock-up since they require expensive PCIe-capable accelerators and are built on top of proprietary PCIe IP and software layers such as Xilinx XDMA [173]. Failure to interface correctly to PCIe can lockup not only the DUT but also the host server machine, requiring remote restart capabilities. In contrast, by leveraging Zynq-based FPGAs [174], Condominium can be employed using only an SSH-capable machine running Vivado and builds upon the BaseJump STL [142] library to provide generic and open bridges to commonly available AXI and UART interfaces. As opposed to using PCIe tunnels for FPGA networking, hardened AXI interfaces on Zyng systems provide direct and low-latency access to design peripherals, such as host DRAM, which can help with high-performance emulation of design that often require low-latency guaranties for on-chip memory access. Furthermore, as opposed to other emulation platforms that, for long-term design development, can easily exceed tens of thousands of dollars, Condominium provides verification teams the ability to begin with the minimal possible Total Cost of Ownership (TCO) and scale costs alongside the design progress. Table 3.1 breaks-down the cost comparison between the prototyping strategies based on recent pricing data. By employing scale-down solutions, such as Condominium, for SW/HW co-design and long-term regression testing and continuous integration, engineers can lower TCO and benefit from higher flexibility and insight into the design, while reserving scale-out for occasional bursts of full-system testing during tape-out events.

By carefully designing the platform interfaces, Condominium provides a flexible environment that can support interactions of emulation design with the outside world without sacrificing emulation accuracy. To that end, great care must be taken to mimic the envi-

<sup>&</sup>lt;sup>1</sup> \$3.3294 per AWS f1.16xlarge hour [7].

<sup>&</sup>lt;sup>2</sup> \$0.4202 per AWS f1.2xlarge hour [7].

<sup>&</sup>lt;sup>3</sup> \$300 per Avnet Ultra96v2 board [18], with a replacement rate of once per three years. Cluster MTBF is 100+ years [178].

ronment between the full design and the subsystem. First, gaining transparency into the emulated subsystem requite run-time streaming of architectural data from RTL to the host system. However, the limited streaming bandwidth can create backpressure that can introduce non-determinism into RTL emulation, making behavior reproducibility impossible. Condominium adheres to strict non-interference of internal design timings through strategic clock-gating during unpredictable host back-pressure. This allows subsystems to execute with the illusion that they are running in situ within the full system. This technique enables the runtime streaming of cycle-accurate RTL data from DUT for the purposes of verification without perturbing the emulation flow. Second, to achieve reproducible testing and realistic performance analysis, accurate timing models should be enforced on IO interfaces with simulated peripherals. Condominium leverages the same clock-gating mechanism to enforce timing guaranties by interfacing with both in-silicon RTL timing models and software hosted abstraction models. By enabling the software or RTL driven abstraction of other parts of the system, including the timing and functional behavior of various peripherals, Condominium can be easily used to fine-tune environmental emulation parameters for better design verification. In section 3.3, we go though Condominium architecture and how it provides an accelerated emulation system without losing cycle-accuracy guaranties.

By providing an accelerated emulation environment with cycle-accurate insight and control over the DUT and its surrounding abstracted system, Condominium has proven to be an extremely powerful tool for agile functional verification and performance optimization of BlackParrot throughout its development. A deep dissection of the subsystem can allow an architect to design experiments to identify subsystem bottlenecks and quickly iterate on potential changes without requiring major microarchitectural changes in the emulation system. In this context Condominium has been used on BlackParrot for instruction-granularity verification through ISA co-simulation, cycle-accurate and time-proportional performance profiling, and accelerated high-fidelity coverage collection for entablement of coverage-guided random verification. Condominium's non-invasive, instrumented measurements and host software abstraction layers were motivated and written for use in BlackParrot, but they are generally applicable to a wide range of hardware projects. In section 3.4, we will go through these use-cases and highlight how Condominium helps architects build and maintain high-quality hardware through facilitating techniques for accurate and agile evaluation.

### 3.3 Condominium Architecture

In this section, we describe the Condominium architecture and how it addresses these challenges cost-effectively and with lower maintenance than previous solutions. The Condominium architecture was designed with the following goals in mind:

• Enable an FPGA-accelerated emulation framework for agile DUT analysis with tight emulation configuration and control mechanism.

- Provide flexible interfaces for precise interfacing between emulated subsystem logic and the abstracted subsystem peripherals.

- Provide cycle-accuracy guaranties to enable reproducibility between RTL simulator and FPGA domains.

- Build an FPGA cluster based on Condominium with remote use capability and robustness against system freezes.

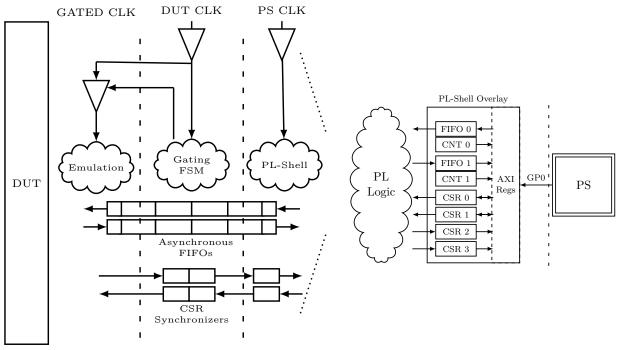

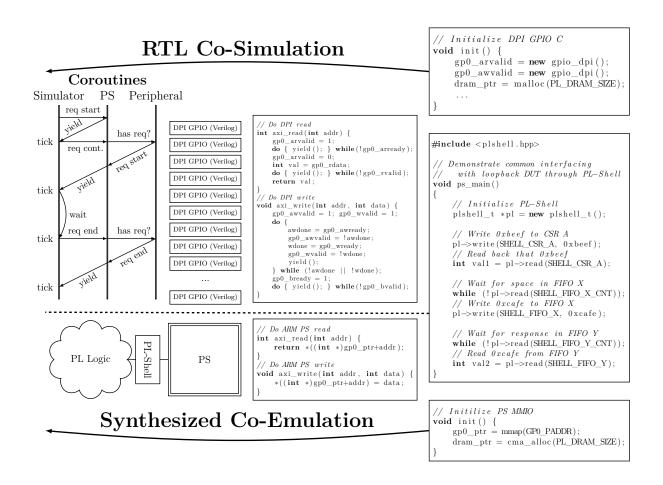

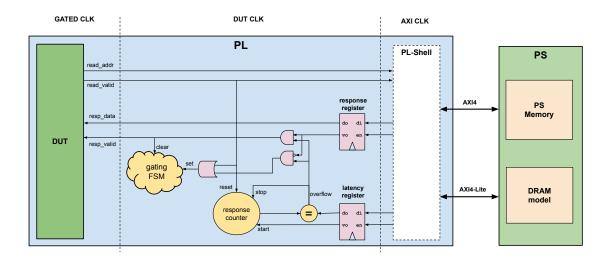

### 3.3.1 Zynq-based Architecture