©Copyright 2025 Huwan Peng

# Methodologies and Architectures for AI Inference Hardware: From Foundational Networks to Large Language Models

Huwan Peng

A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

University of Washington

2025

Reading Committee:

Michael Taylor, Chair

C.J. Richard Shi, Chair

Ang Li

Program Authorized to Offer Degree: Electrical and Computer Engineering

#### University of Washington

#### Abstract

Methodologies and Architectures for AI Inference Hardware: From Foundational Networks to Large Language Models

#### Huwan Peng

Co-Chairs of the Supervisory Committee:

Professor Michael Taylor

Electrical and Computer Engineering

Professor C.J. Richard Shi Electrical and Computer Engineering

The rapid advancements in large language models (LLMs) have significantly reshaped the artificial intelligence landscape, enabling transformative applications. However, these developments pose profound challenges for hardware architectures, particularly concerning performance, efficiency, and scalability. This dissertation investigates these critical challenges, proposing novel methodologies and architectural designs for specialized hardware, with a primary focus on optimizing large-scale LLM inference.

Core contributions of this thesis include the development of ReaLLM and Chiplet Cloud. ReaLLM is a holistic simulation framework for LLM serving, designed to bridge detailed accelerator-level insights with system-wide performance evaluations. This framework facilitates rapid exploration and precise simulation of both hardware architectures and software strategies. Chiplet Cloud is a cloud-scale architecture optimized for the Total Cost of Ownership (TCO) of LLM inference. Its key architectural innovations include fitting model parameters within on-chip memory to improve performance, co-optimizing chip size with software mapping to reduce TCO, and effectively exploiting model sparsity to support larger models.

Additionally, the thesis discusses ChronoStack, a 3D memory architecture developed as part of a collaborative research effort, featuring a novel Time-Multiplexed KV-Prefetching

technique, specifically optimized for the demands of long-context LLMs. The dissertation also incorporates foundational research on accelerators for earlier AI paradigms, including Convolutional Neural Networks (CNNs), Recurrent Neural Networks (RNNs), and deep reinforcement learning, providing a broad perspective on AI hardware evolution.

Together, this body of work presents a detailed investigation into architectures and methodologies for AI inference hardware, tracing a clear progression from foundational network acceleration to modern large language model serving. The research aims to contribute novel approaches and critical insights towards achieving efficient, high-performance computing for the advancing field of artificial intelligence.

### TABLE OF CONTENTS

|           |                                                                                      | Pa  | ıge |

|-----------|--------------------------------------------------------------------------------------|-----|-----|

| List of I | Figures                                                                              |     | iii |

| Chapter   | 1: Introduction                                                                      |     | 1   |

| Chapter   | 2: Background                                                                        |     | 5   |

| 2.1       | Fundamentals of Early Models                                                         |     | 5   |

| 2.2       | Fundamentals of Large Language Models                                                |     | 8   |

| 2.3       | System Techniques for AI Inference                                                   |     | 14  |

| 2.4       | Specialized Hardware Acceleration                                                    |     | 19  |

| Chapter   | 3: Foundational Work: Accelerating Early AI Paradigms                                |     | 25  |

| 3.1       | iFPNA: A Flexible and Efficient Deep Learning Processor in $28\mathrm{nm}$ CMOS $$ . |     | 25  |

| 3.2       | F B C: Optimized Deep Q-Learning with the Filter-Batch-Channel Dataflow              |     | 31  |

| 3.3       | Conclusion                                                                           |     | 48  |

| Chapter   | 4: ReaLLM: A Holistic Hardware System Simulation Framework for LLM Serving           |     | 49  |

| 4.1       | Introduction                                                                         |     | 49  |

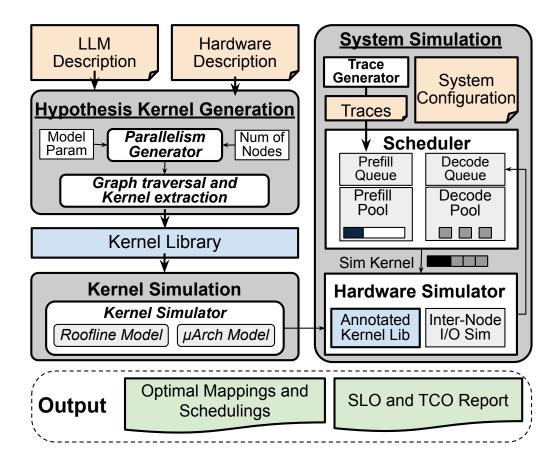

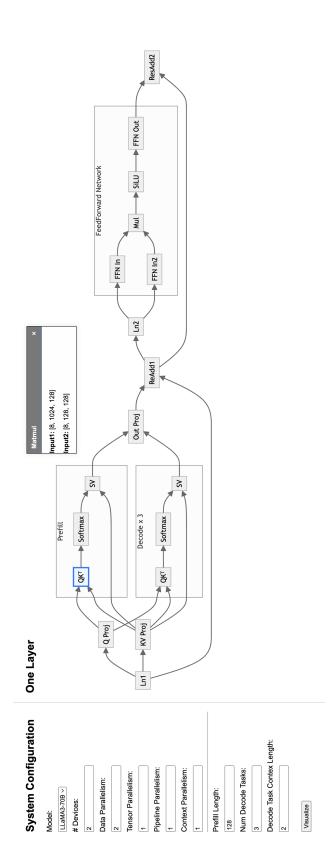

| 4.2       | Framework Architecture and Core Components                                           |     | 53  |

| 4.3       | Device-level Modeling and Kernel Profiling                                           |     | 60  |

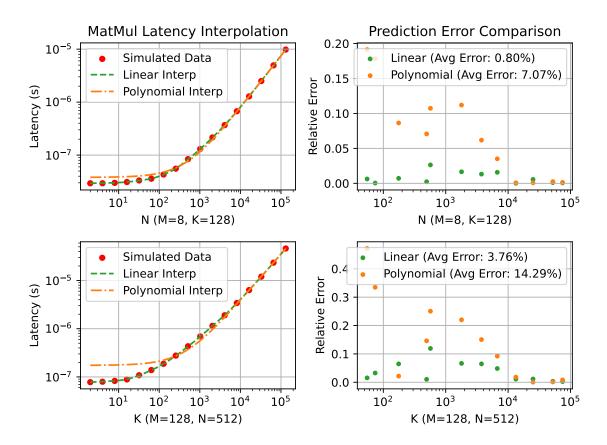

| 4.4       | System-level Modeling and Trace-Driven Simulation                                    |     | 66  |

| 4.5       | Validation and Evaluation                                                            |     | 73  |

| 4.6       | Discussion and Conclusion                                                            |     | 81  |

| Chapter   | 5: Chiplet Cloud: A TCO-Optimized LLM Hardware Architecture                          |     | 84  |

| 5.1       | Introduction                                                                         |     | 84  |

| 5.2       | Chiplet Cloud Architecture                                                           |     | 86  |

| 5.3       | Case Studies                                                                         |     | 92  |

| 5.4       | Evaluation                                                                           |     | 97  |

| 5.5       | Conclusion                                                                           | . 1 | 01  |

| Chapter   | 6: ChronoStack: A 3D-Memory Architecture for Long-Context LLM 104 |

|-----------|-------------------------------------------------------------------|

| 6.1       | Introduction                                                      |

| 6.2       | KV-Prefetching to Address Memory Bottlenecks                      |

| 6.3       | Hybrid Bonding 3D DRAM Accelerator                                |

| 6.4       | Evaluation                                                        |

| 6.5       | Conclusion                                                        |

| Chapter   | 7: Conclusion                                                     |

| 7.1       | Summary of Research and Contributions                             |

| 7.2       | Future Work                                                       |

| Bibliogra | aphy                                                              |

## LIST OF FIGURES

| Figure 1 | Number                                                                                                                                                               | Page |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.1      | Tensors and operations in three phases of a convolutional layer are shown in the block diagram and loop nest, with a unified pattern                                 | . 9  |

| 2.2      | The decoder-only transformer model architecture.                                                                                                                     | . 10 |

| 2.3      | Key operations in a transformer block with grouped-query attention and SwiGLU activation function                                                                    | . 13 |

| 2.4      | Comparison of mixed continuous batching (MCB) and chunked mixed continuous batching (C-MCB)                                                                          | . 17 |

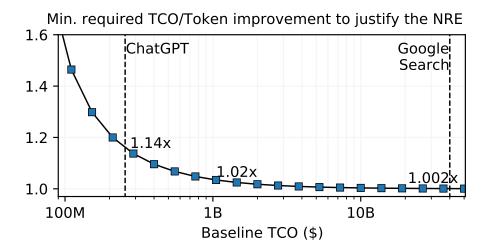

| 2.5      | Minimum TCO/Token improvement required from an ASIC to justify NRE costs as a function of baseline TCO on existing hardware                                          | . 24 |

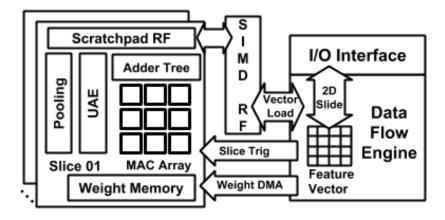

| 3.1      | The iFPNA architecture                                                                                                                                               | . 26 |

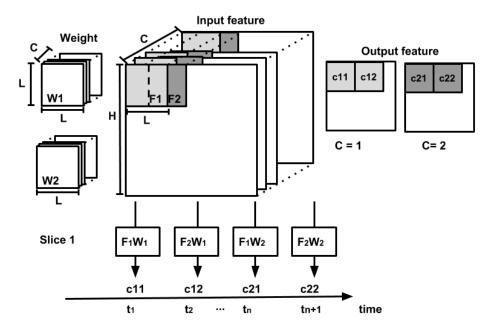

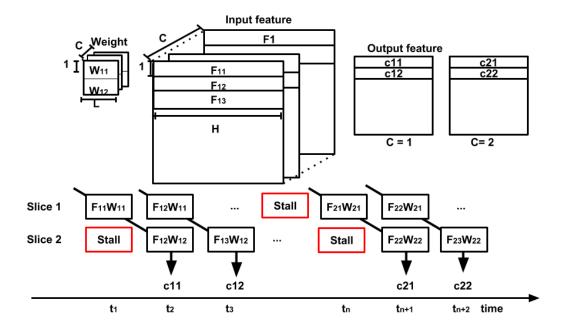

| 3.2      | Weight Stationary on the iFPNA architecture                                                                                                                          | . 29 |

| 3.3      | Input Stationary on the iFPNA architecture                                                                                                                           | . 29 |

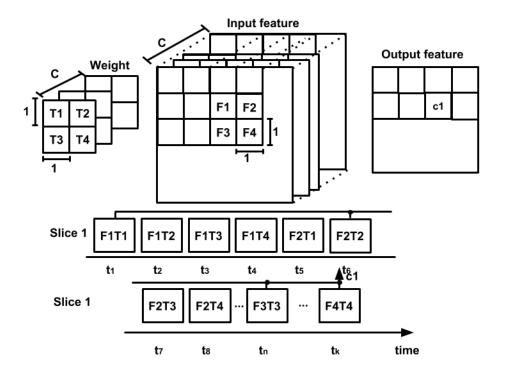

| 3.4      | Row Stationary on the iFPNA architecture                                                                                                                             | . 30 |

| 3.5      | Tunnel Stationary on the iFPNA architecture                                                                                                                          | . 30 |

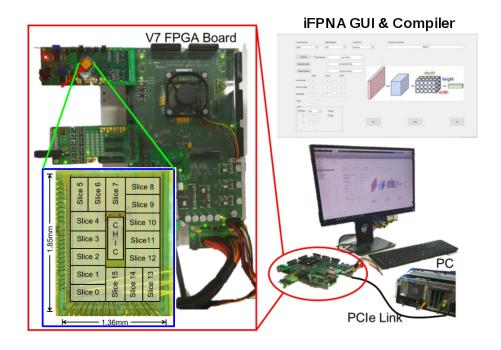

| 3.6      | iFPNA chip prototype and demonstration system                                                                                                                        | . 31 |

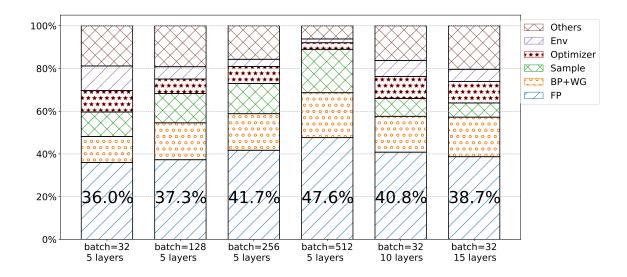

| 3.7      | End-to-end of Rainbow DRL latency breakdown on a GPU. DNN inferences (FP) account for 36.0% to 47.6% of latency.                                                     | . 33 |

| 3.8      | A study of popular DRL algorithms. With the large number of training iterations, DRL often uses a shallow DNN and the layer shape varies greatly.                    | 34   |

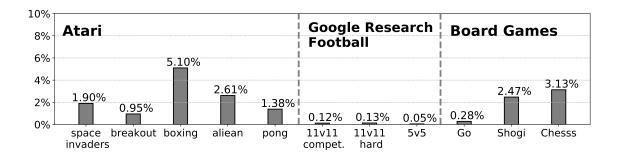

| 3.9      | Change rate of adjacent frames                                                                                                                                       | . 35 |

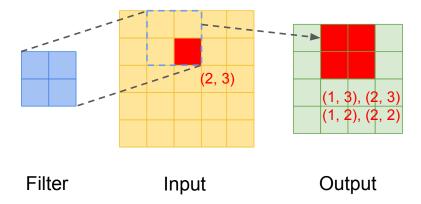

| 3.10     | The different output indexes can be derived based on different input indexes.                                                                                        | 36   |

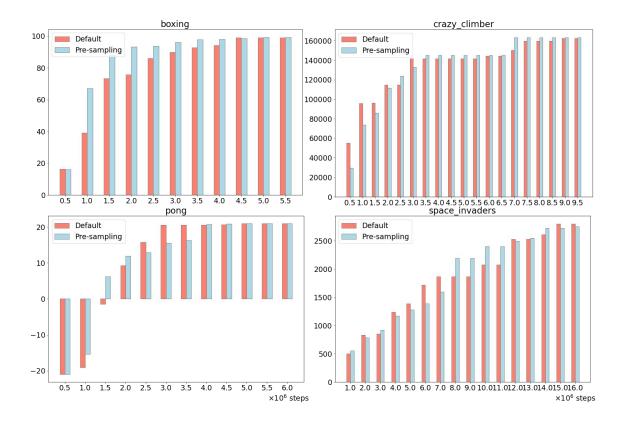

| 3.11     | The training speed differences when applying different sampling scheme. X-axis represents training steps, Y-axis represents achieved scores during the               |      |

|          | training.                                                                                                                                                            | . 37 |

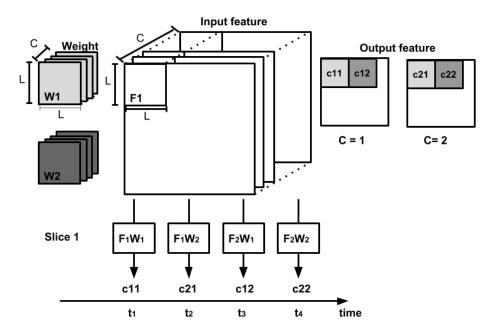

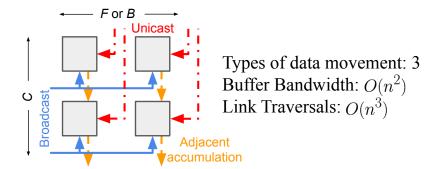

| 3.12     | F C and $B C$ dataflows require a variety of complex data movements, leading to high design and control overhead                                                     | . 38 |

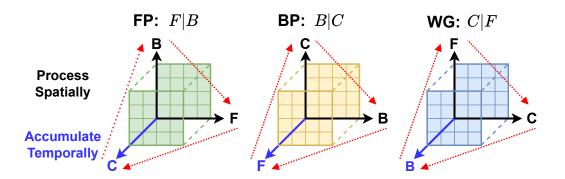

| 3.13     | In F B C, at either phase of FP, BP, or WG, the two dimensions from $F$ , $B$ , and $C$ are processed in parallel, and the other dimension is accumulated temporally | . 39 |

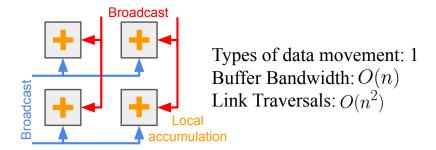

| 3.14 | F B C has less and simple data movements, leading to low design and control overhead, so it has good scalability                                                                                                                                                                   | 40 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

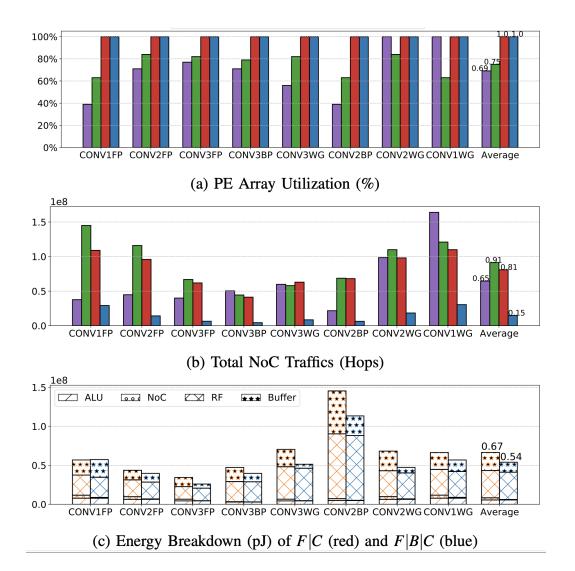

| 3.15 | Compared with $R_y E_y$ , $F C$ , and $E_x E_y$ on a $32\times32$ PE Array, $F B C$ achieves 100% utilization, needs less NoC traffics and costs less energy in most cases                                                                                                         | 42 |

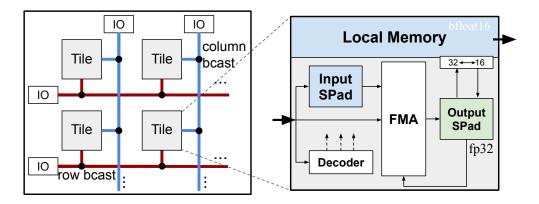

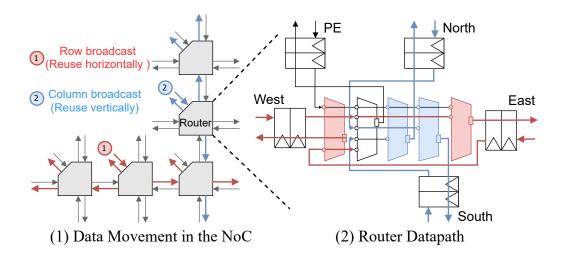

| 3.16 | A high-level DRLP diagram and the tile with mixed-precision MACs. Tiles are connected by two sets of 1D broadcast NoC to enable the $F B C$ dataflow.                                                                                                                              | 43 |

| 3.17 | (1) In most cases, data read from a tile will be broadcast to the whole row (red arrows) to reuse horizontally or the whole column (blue arrows) to reuse vertically. (2) shows the datapath inside each 1D broadcast router                                                       | 44 |

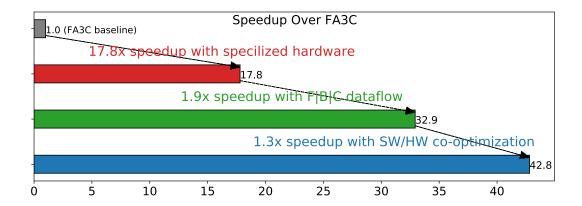

| 3.18 | Speedup breakdown of DRLP over FA3C. $F B C$ data<br>flow and co-optimization bring 1.9× and 1.3× speedup, respectively                                                                                                                                                            | 45 |

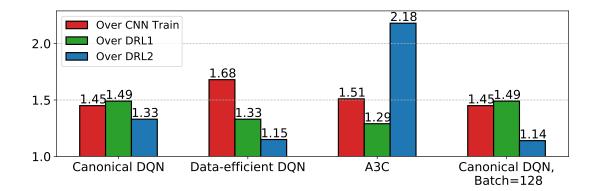

| 3.19 | Speedup of DRLP over optimistically scaled CNN training accelerator (CNN Train) [33], DRL accelerators [206] (DRL1) and [99] (DRL2) on DNNs training in different DRL algorithms. DRLP achieves speedups of up to $1.68\times$ , $1.49\times$                                      |    |

|      | and 2.18×                                                                                                                                                                                                                                                                          | 46 |

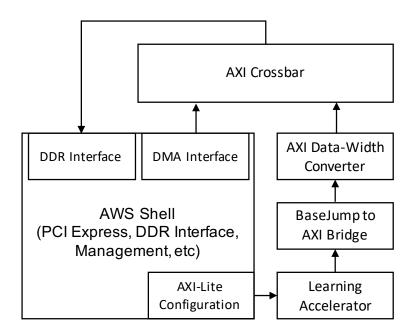

| 3.20 | Block diagram of accelerator integrated with the AWS EC2 F1 shell                                                                                                                                                                                                                  | 47 |

| 4.1  | High-level overview of the ReaLLM simulator pipeline                                                                                                                                                                                                                               | 56 |

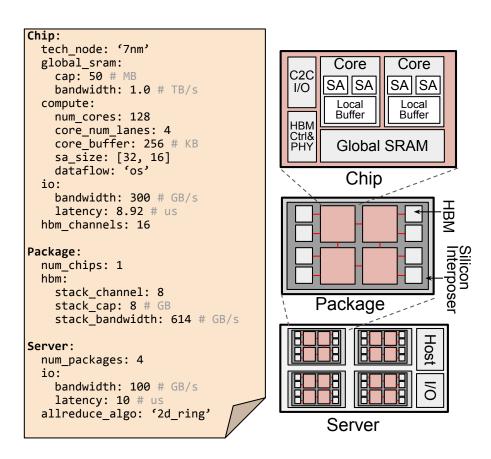

| 4.2  | Example of ReaLLM's abstract hardware description hierarchy, depicting chip, package, and server level components and their parameterization                                                                                                                                       | 57 |

| 4.3  | The web-based Graphical User Interface of ReaLLM                                                                                                                                                                                                                                   | 59 |

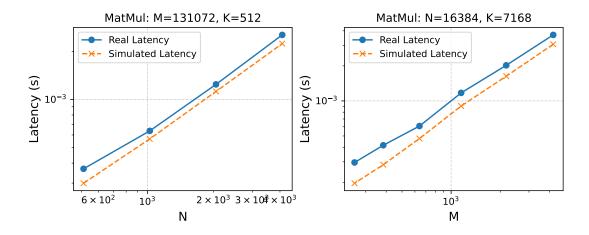

| 4.4  | Comparison of MatMul latency interpolation methods. (Left) Simulated latency data points (red dots) with linear and polynomial interpolation. (Right) Relative prediction error for linear and polynomial interpolation. Linear interpolation generally achieves lower error rates | 67 |

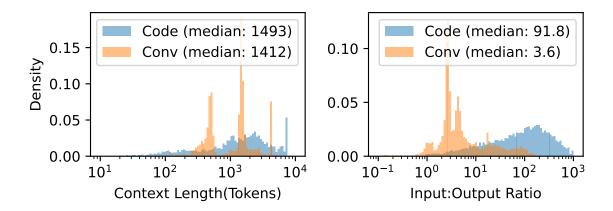

| 4.5  | Distribution of context lengths and input-to-output token ratios for coding and conversational tasks, derived from the Azure LLM Inference Dataset [126].                                                                                                                          | 69 |

| 4.6  | Validation of kernel latency predictions on A100. Each subfigure compares real and simulated latencies for MatMul at different input sizes                                                                                                                                         | 73 |

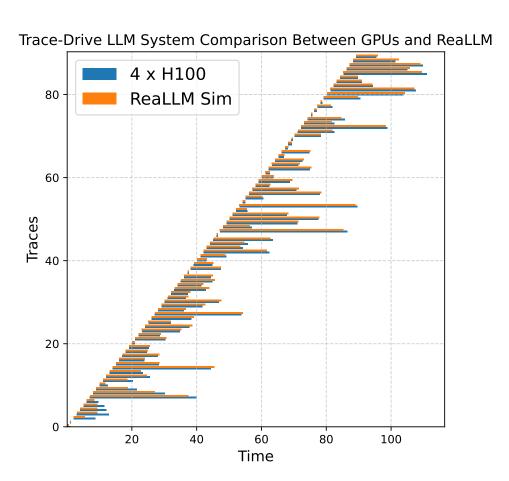

| 4.7  | Comparison of simulated and real end-to-end request latencies for LLaMA-70B inference on a four-H100 system                                                                                                                                                                        | 75 |

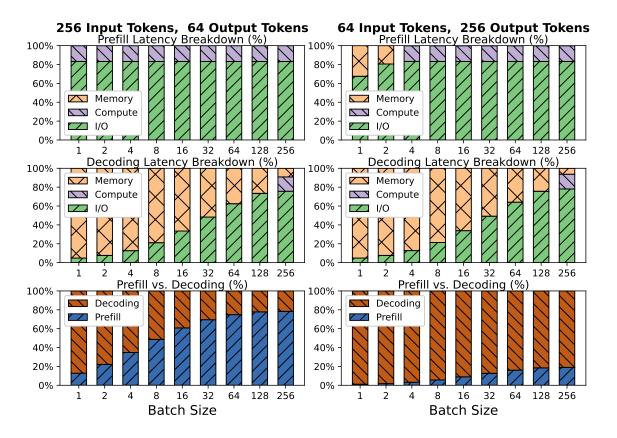

| 4.8  | Latency breakdown of 64 TPU v5p chips. The system is IO-bound in prefill (top row), and memory-bound for most batch sizes while decoding (second row). Decoding often has longer latency than the prefill (bottom row)                                                             | 76 |

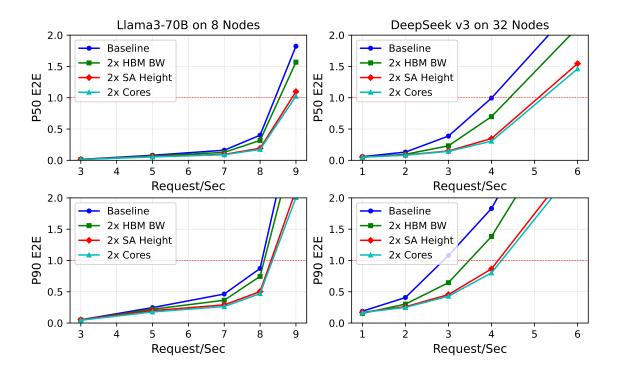

| 4.9  | Latency metrics across input loads of Llama3-70B on 8 nodes (left) and DeepSeek v3 on 32 nodes (right) systems with different architectures                                                                                                                                        | 79 |

| 4.10 | TTFT and E2E across input loads of Llama3-70B for conversation applications on a 32-node system with different architectures                                                                                                                                                       | 80 |

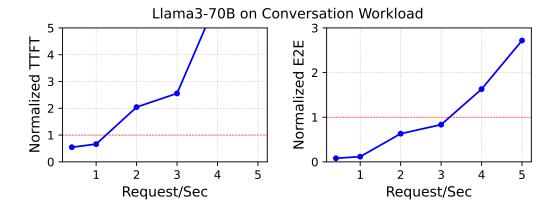

| 4.11 | ReaLLM achieves a $164\times$ speedup in trace simulation time compared to the baseline kernel simulator by leveraging precomputed kernel reuse                                                                                                                                                                                                                                                           | 81  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

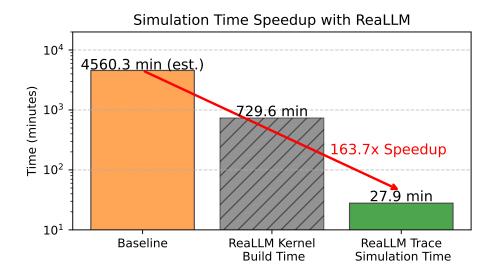

| 5.1  | Compared to conventional systems, Chiplet Cloud (1) fits all model parameters inside the on-chip CC-MEM, greatly improving the performance; (2) co-optimizes the chip size with software mapping to reduce TCO/Perf; (3) exploits sparsity to reduce TCO and support larger models                                                                                                                        | 85  |

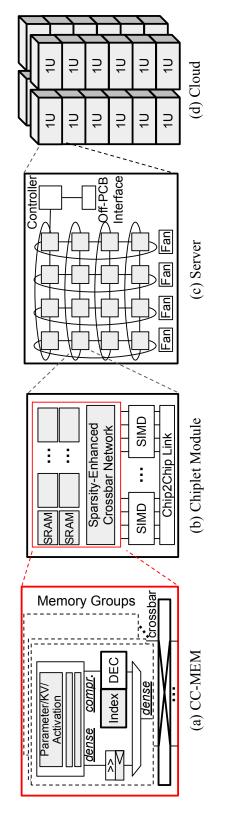

| 5.2  | Chiplet Cloud architecture from the CC-MEM to the cloud                                                                                                                                                                                                                                                                                                                                                   | 87  |

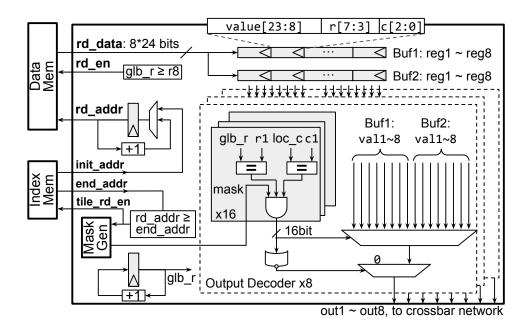

| 5.3  | Compression decoder unit in CC-MEM                                                                                                                                                                                                                                                                                                                                                                        | 90  |

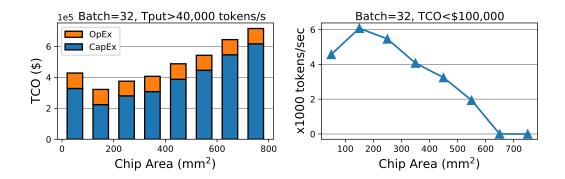

| 5.4  | Proper chip size can reduce the fabrication costs (CapEx) without compromising performance as much. Left: For a given throughput requirement, chips with a size of less then 200 mm² have lowest TCO. Right: For a given TCO budget, chips with a size between 100 mm² to 200 mm² achieve the best throughput                                                                                             | 94  |

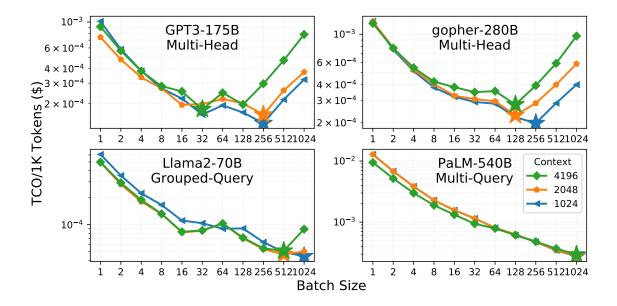

| 5.5  | The optimal TCO/Token under different batch sizes. Small batch requires less silicon, and large batch benefits weight reuse. The optimal batch size for multi-head models is between 32 to 256, while the multi-query and grouped-query models are able to maintain a near-optimal TCO/Token at batch size 1024                                                                                           | 95  |

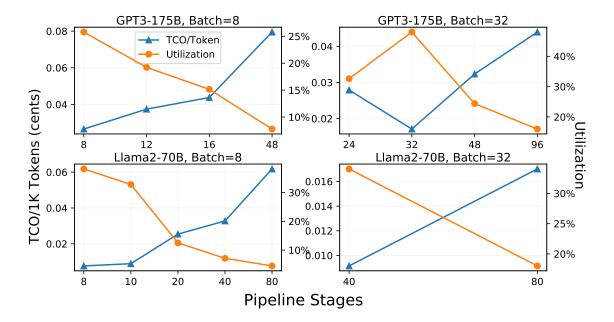

| 5.6  | Pipeline stages sweeping for different models and batch sizes. The number of pipeline stages close to the batch size usually achieves the highest utilization, resulting in the optimal $TCO/Token.$                                                                                                                                                                                                      | 96  |

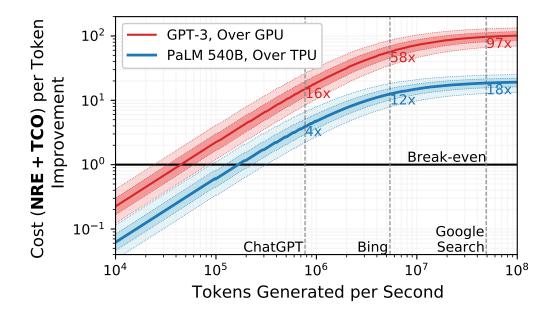

| 5.7  | Compared to A100 GPU and TPUv4, Chiplet Cloud can achieve over $97\times$ and $18\times$ improvement in (NRE+TCO)/Token on GPT-3 and PaLM 540B, respectively. The light and dark shaded regions represent the results under $\pm 30\%$ and $\pm 15\%$ input variance                                                                                                                                      | 98  |

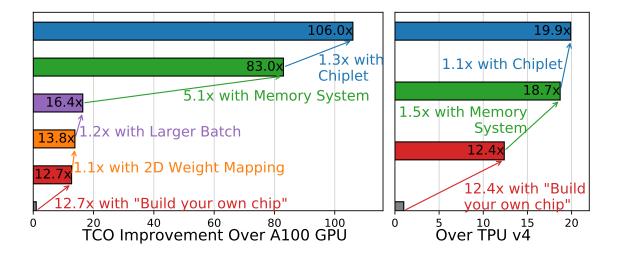

| 5.8  | TCO/Token improvement breakdown over GPU and TPU. $\ \ldots \ \ldots \ \ldots$                                                                                                                                                                                                                                                                                                                            | 99  |

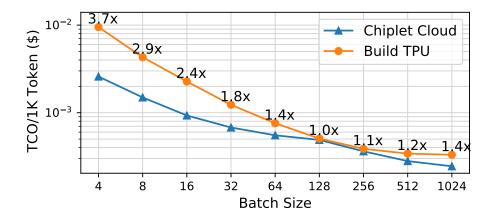

| 5.9  | Chiplet Cloud is more efficient than TPU v4 at most batch sizes, especially for small batch sizes. TPU performance is from [150] with and TCO is from our model                                                                                                                                                                                                                                           | 100 |

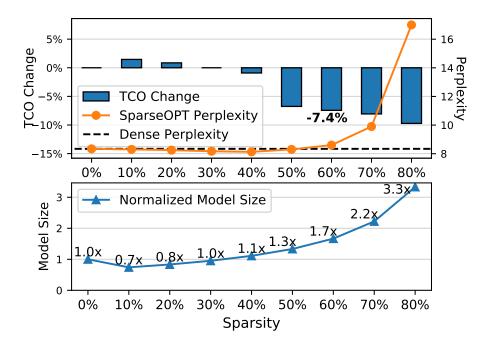

| 5.10 | Top: TCO/Token and perplexity (from SparseGPT [52], lower is better) of OPT-175B under different sparsity. Chiplet Cloud can further reduce 7.4% of TCO/Token at $60\%$ sparsity with negligible increase in perplexity. Bottom: Chiplet Cloud supports a $1.7\times$ larger model with a sparsity of $60\%$                                                                                              | 100 |

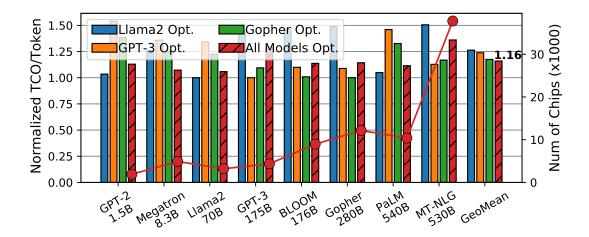

| 5.11 | A Chiplet Cloud chip design is flexible to run models of different sizes via scale-up. Comparing to the model-optimized design, chip optimized for other models has TCO/TOken of $1.1\times$ to $1.5\times$ (blue, orange and green bar). One can also optimizes the chip for multi-model (dashed red bars) at only $1.16\times$ TCO/Token on average, and the number of chips used is shown in red dots. | 102 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                           |     |

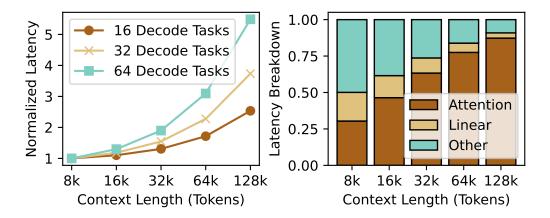

| 6.1  | The normalized latency and breakdown of a chunked mixed continuous batching kernel. Prefill chunk size set to 512. Left: As the context length increases, benefits of batching decode tasks diminishes even with a prefill chunk helping the operational intensity of linear operations. Right: Breakdown for 32 decode tasks. As the context length grows the attention layer                                                                                                                                                                            |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

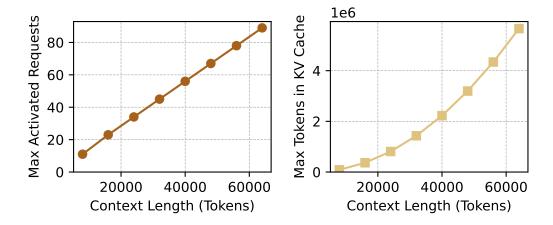

| 6.2  | Left: For a constant request rate, as the context length grows so does the peak number of active requests being processed, because longer request it takes more iterations to finish. Right: KV Cache grows super linear with context length since there more active requests and each request is longer 108                                                                                                                                                                                                                                              |

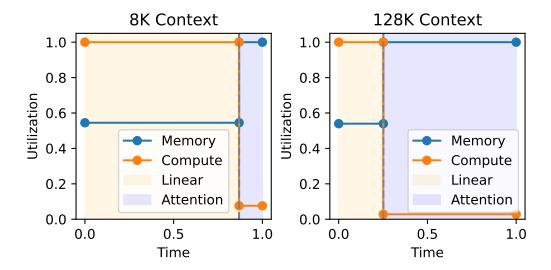

| 6.3  | In linear operations, LLM inference is often compute-bound and underutilizes memory bandwidth, while in attention operations, it is memory-bound and underutilizes compute cores. As the context length increases, attention operations take longer time. Figure generated based on roofline model with a chunk size of 512                                                                                                                                                                                                                               |

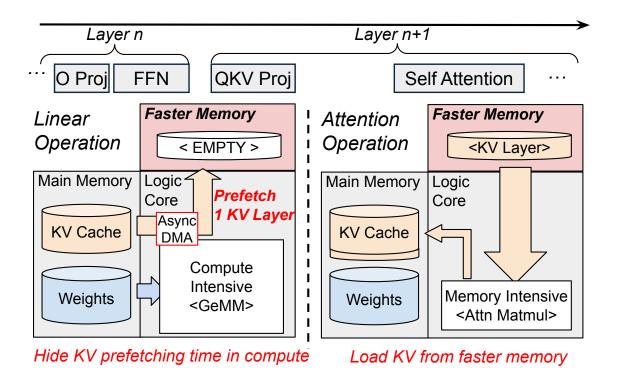

| 6.4  | Time-Multiplexed KV-Prefetching overview. While performing compute bounded linear operations, we opportunistically move the KV cache of the next attention operation to a faster memory. The attention operation operates entirely out of the faster memory reduce the overall latency with only a small update for new KV cache values back to main memory                                                                                                                                                                                               |

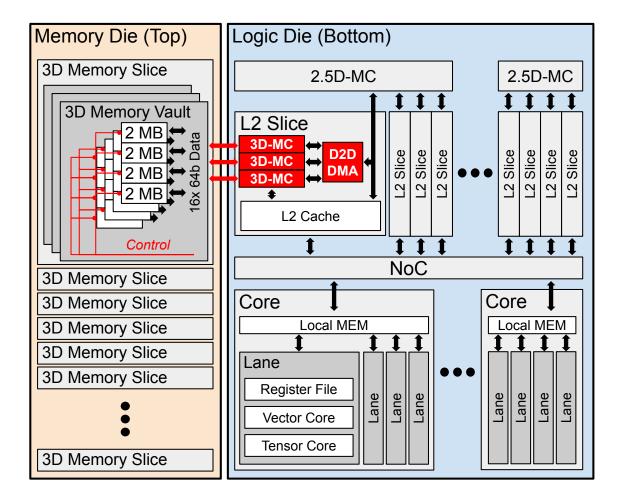

| 6.5  | Architectural overview of ChronoStack. The logic die sits below the memory die. The logic die is composed of SIMD cores that use both vector and tensor processing units for the computation. These cores talk with the L2 cache over an on-chip network. The L2 cache is organized as slices with each slice containing a portion of the L2 cache, a DRAM-to-DRAM DMA controller, as well as 3D memory controller. The memory die is organized into slices with multiple memory vaults per slice corresponding to the 3D memory controllers per L2 slice |

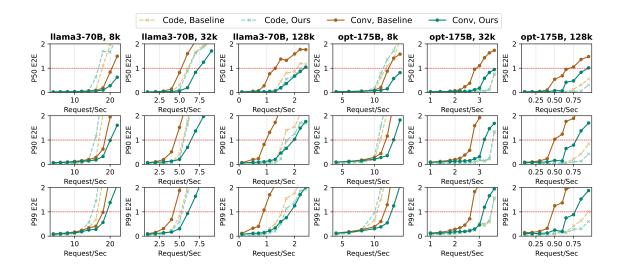

| 6.6  | E2E comparison of proposed and baseline system across input request rates. Different columns of the graph represent different models and maximum context lengths. Dashed red lines indicate E2E SLO                                                                                                                                                                                                                                                                                                                                                       |

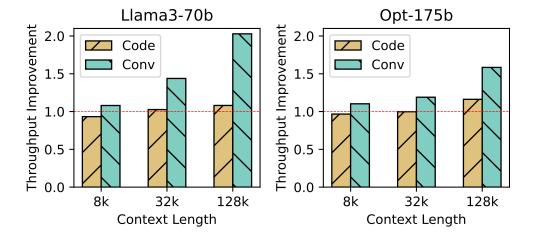

| 6.7  | End-to-end throughput improvement. Throughput is measured as the maximum input request rate while the system still meets the E2E SLO 117                                                                                                                                                                                                                                                                                                                                                                                                                  |

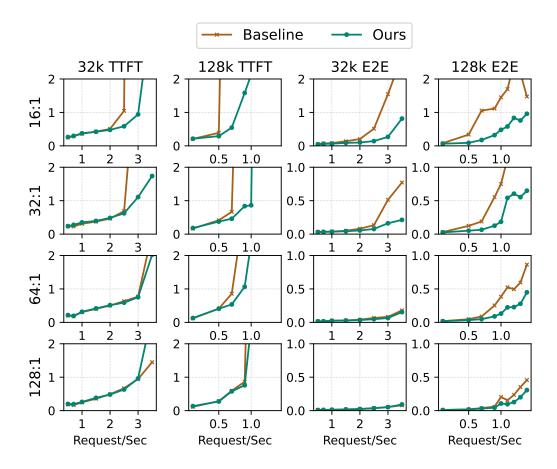

| 6.8  | Llama3-70B P90 TTFT and E2E latency for 32K and 128K context lengths and different input-output ratios                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

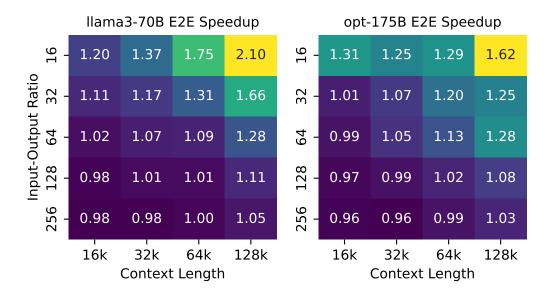

| 6.9  | Throughput improvement of the proposed system over the baseline given different context lengths and input-output ratios                                                                                                                                                                                                                                                                                                                                                                                                                                   |

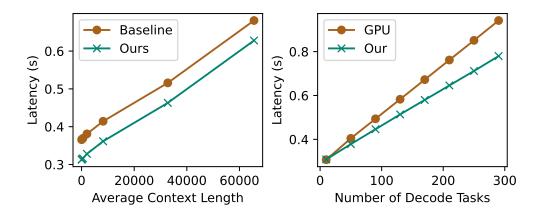

| 6.10 | Latency comparison of DeepSeek V3. Left: Latency vs. average context length per decode task. Right: Latency vs. number of concurrent decoding tasks. ChronoStack consistently outperforms GPU, with increasing benefits as number of decode task grows                                                                                                                                                                                                                                                                                                    |

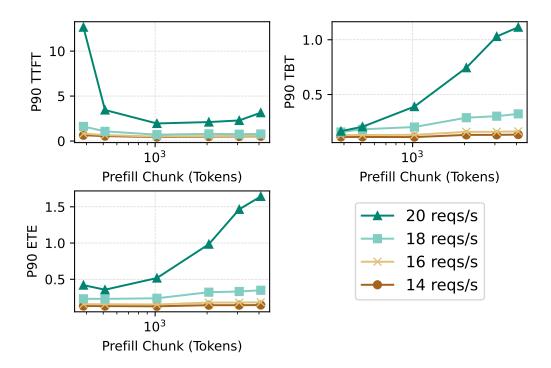

| 6.11 | Latencies across different chunk sizes for Llama3-70B at 8K context. Small    |

|------|-------------------------------------------------------------------------------|

|      | prefill chunk sizes reduce TTFT and increase TBT, while affecting E2E. $$ 121 |

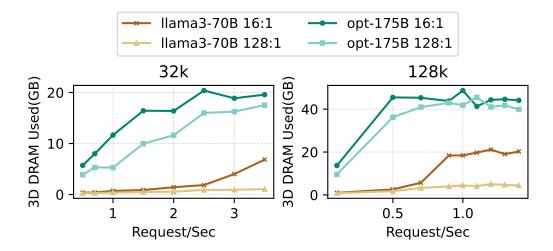

| 6.12 | 3D memory usage in the system. 3D memory usage in the system. Higher          |

|      | input loads use more 3D memory due to more concurrent tasks. Multi-head       |

|      | models require more memory than grouped-query model                           |

#### ACKNOWLEDGMENTS

Completing this PhD journey feels surreal. Though I've imagined this moment countless times, it is still hard to believe that it has finally arrived. One of my greatest motivations to persevere through the challenges was precisely this chance—to formally thank the many incredible individuals who have supported me along the way.

First and foremost, my deepest gratitude goes to my advisors, Professor Richard Shi and Professor Michael Taylor. My journey into the world of research began with Richard nearly a decade ago, during my undergraduate years. His guidance was instrumental in sparking my passion for this field, and I am immensely thankful for his mentorship. Michael has profoundly shaped me as a researcher, teaching me not just the intricacies of research but also the skills of effective writing, presenting, and handling public discourse.

I am also grateful to my committee members, Professor Ang Li and Professor James Zhang, for their insightful feedback and for dedicating their time to my doctoral work.

Throughout my PhD, I have been fortunate to learn from and collaborate with exceptional mentors and colleagues. I owe a special thanks to Professor Chixiao Chen. Leading a small and relatively inexperienced team, including myself, to successfully tape out two chips in such a short period was an incredible feat. His dedication, hard work, and passion for his research were truly inspiring, and I cherish the memories of our time working together. I must also extend a heartfelt thank you to Scott Davidson. Though a fellow PhD student, Scott is one of the most knowledgeable individuals I have ever met. I thoroughly enjoyed every conversation we had and deeply value our collaboration and friendship. My gratitude also goes to my other esteemed collaborators: Professor Dustin Richmond, Professor Shuaiwen Leon Song, Ameen Akel, and Xingyao Zhang. Their contributions and insights have been invaluable. I also want to thank Timothy Heil, my manager during my internship at Microsoft, for the guidance and opportunities he provided.

At UW, I was fortunate to be part of two exceptional research groups: SSRL and BSG. These communities provided not only intellectual stimulation but also lasting friendships. Many thanks to Hongwei Ding, Ailing Piao, Professor Aili Wang, Chang Liu, Rongjin Xu, and Jialin Wang from SSRL. A special acknowledgment goes to Cindy Liu, with whom mutual encouragement helped us both reach this finish line. From BSG, I warmly thank Shaolin Xie, Chun Zhao, Paul Gao, Dan Petrisko, Tommy Jung, Farzam Gilani, and Rico Li. I want to offer a special word of encouragement to Yuan-Mao Chueh and Anoop Mysore. You are both talented researchers and wonderful friends; keep pushing forward, your hard work will undoubtedly pay off.

Outside of academia, I am blessed with many supportive friendships. Xiyang Liu has been an invaluable friend throughout this journey, particularly during the challenging COVID-19 period. Our weekend hangouts were often the only moments of relaxation during those challenging times. His serious approach to both research and life has been a source of inspiration. Thanks also to my landlord Ms. Wu and my roommate Tom, whose kindness and support have greatly eased my daily life. A special thank you to the Seattle United Running Club. The warmth and friendliness of everyone I met there made me feel at home in a foreign land for the first time. There are so many other friends who offered help and support along the way, and I am wholeheartedly thankful for each and every one of you, even if I cannot list all of your names here.

My deepest and most heartfelt gratitude goes to my family. To my parents, thank you for your unconditional love and unwavering support. It has been a source of regret that I have been away from home for so long and unable to visit as much as I would have liked during my PhD. Despite the distance, I have always felt your love, and it has been a constant source of strength.

Last, but certainly not least, I want to thank my beloved wife, Xuanfeng. Your constant support, understanding, and respect as I pursued this often lonely path have meant everything to me. For most of this journey, we were separated by nations, and I know you endured your own difficult and lonely times. You are more resilient and stronger than I am. Thank

you for believing in me, even during moments when I doubted myself. This achievement is as much yours as mine. It is, profoundly and unequivocally, all because of you.

Portions of this work were partially supported by Air Force Research Laboratory (AFRL) and Defense Advanced Research Projects Agency (DARPA) under agreement numbers FA8650-18-2-7863 and FA8650-18-2-7856; NSF grants SaTC-1563767, SaTC-1565446. This work intersects and leverages research and infrastructure created by the members of the Bespoke Silicon Group, spanning across accelerators ([20, 53, 221, 210, 142, 140, 224, 17, 204, 162, 61, 175, 10, 163, 60, 62, 95, 203, 13]), ML ([202]), ASIC Clouds ([194, 211, 191, 181, 96, 97, 124, 183]), open source hardware ([193, 184, 50]) RISC-V ([147, 159, 158, 42, 223, 7, 201, 88, 156, 130, 35, 155, 115, 91]), Network-on-Chips ([89, 148, 226, 188, 101]), security ([23, 12, 22, 69, 70, 8]), benchmark suites ([196, 105, 14]), dark silicon ([180, 179, 180, 182, 18, 63, 60, 203]), multicore ([31, 30, 147, 67, 65, 66, 178, 188, 190, 185, 177, 101, 186, 189, 187, 205]), compiler tools ([82, 56, 80, 58, 81, 79, 57, 218, 2, 11]) and FPGAs ([225, 76, 14]).

# DEDICATION

To my mother, Xiuhong Hu.

#### Chapter 1

#### INTRODUCTION

The last decade has seen significant advancements in the capabilities and applications of Artificial Intelligence (AI), leading to transformative changes across various sectors. From influencing industries like healthcare and finance to enabling everyday applications such as natural language translation, recommendation systems, and autonomous vehicles, AI is increasingly impacting modern life [160]. Central to these advancements are sophisticated machine learning models, particularly Deep Neural Networks (DNNs), which have demonstrated notable performance across a spectrum of complex tasks [114].

The trajectory of AI progress has been characterized by a trend towards developing larger and more complex models. While foundational network architectures like Convolutional Neural Networks (CNNs) and Recurrent Neural Networks (RNNs) established key principles, the recent emergence of Large Language Models (LLMs) such as GPT-3 [21], PaLM [34], and Llama [197] has enabled significant progress in natural language understanding, generation, and reasoning. These models, often comprising hundreds of billions or even trillions of parameters [51], generally follow scaling laws which suggest that model performance improves with increased scale (data, parameters, and computation) [93]. However, this demand for increased scale translates directly into substantial growth in computational requirements for both training these models and, importantly, for deploying them for inference at scale. The computational power needed to serve these models to many users in real-time presents a significant challenge, straining existing hardware infrastructure and impacting operational costs and energy consumption.

The computational support for the current AI developments has largely been provided by general-purpose hardware, primarily Central Processing Units (CPUs) and Graphics Processing Units (GPUs). While CPUs offer flexibility, their architecture is not ideally suited for the massively parallel computations that are prevalent in AI workloads. GPUs, origi-

nally developed for graphics rendering, have been widely adopted for AI due to their parallel processing capabilities and have become common solutions for training and deploying many AI models [133, 134]. However, as AI models, especially LLMs, continue to grow in size and complexity, the limitations of these general-purpose architectures are becoming more evident. GPUs, despite their power, retain overheads from their general-purpose design and may not provide the optimal balance of performance, power efficiency, and cost when deployed at the scale required by modern AI services. A key challenge is the memory wall, where the rate of improvement in processor speed has outpaced improvements in memory bandwidth and latency [208]. LLM inference, characterized by large model sizes and substantial intermediate data (such as the KV cache in Transformers [200]), is often memory-bandwidth bound, particularly during the token generation phase [150]. This can lead to underutilization of compute units and reduce overall system efficiency. Furthermore, the energy consumption associated with running these large models on general-purpose hardware at scale raises considerations regarding environmental sustainability and economic viability [144].

To address the performance, efficiency, and scalability limitations of general-purpose hardware, the development of Application-Specific Integrated Circuits (ASICs) tailored for AI workloads has become an important direction [176]. ASICs offer the potential for substantial improvements in performance and energy efficiency by designing hardware specifically optimized for the computational patterns and data movement characteristics of AI algorithms, such as matrix multiplications, convolutions, and attention mechanisms. By removing unnecessary general-purpose logic and co-designing the architecture with the target algorithms, AI ASICs can achieve higher throughput and lower power consumption per operation [157]. While the Non-Recurring Engineering (NRE) costs associated with ASIC design are considerable [98], the large volume of computations required for large-scale LLM deployment can make this investment practical. The significant operational Total Cost of Ownership (TCO) of running LLM inference on existing hardware means that even moderate improvements in TCO per token, offered by a specialized ASIC, can lead to considerable savings, potentially amortizing the NRE costs. These economic factors, along with the continued demand for AI, are driving the development of specialized AI hardware.

The primary objective of this doctoral research is:

To design and evaluate high-performance and efficient ASIC accelerator architectures and supporting methodologies for diverse and evolving AI applications, with a primary focus on Large Language Models.

This dissertation examines the challenges in AI hardware and presents methodologies and architectural designs to address them. The work is organized as follows, with each chapter detailing specific contributions toward this goal:

- Chapter 2: Background provides an overview of fundamental AI models, including

early paradigms like CNNs, RNNs and deep reinforcement learning, as well as the

architecture of modern Large Language Models. It also discusses system techniques

for AI inference, principles of specialized hardware acceleration, and the economic

considerations motivating ASIC development.

- Chapter 3: Foundational Work: Accelerating Early AI Paradigms details initial research on accelerating earlier AI workloads. This chapter discusses contributions to the development of iFPNA [26, 25], a flexible deep learning processor adaptable to various network types, and presents DRLP, a specialized accelerator for Deep Q-Learning that introduced the efficient F|B|C (Filter-Batch-Channel) dataflow. This foundational work provided insights into architectural flexibility, dataflow optimization, and hardware-software co-design relevant to subsequent research.

- Chapter 4: RealLM: A Holistic Simulation Framework for LLM Serving introduces RealLM, a comprehensive, multi-level hardware system simulation framework developed to address the complexity of evaluating modern LLM inference systems [146]. It is designed to bridge detailed accelerator-level insights with system-wide performance evaluations, enabling exploration and simulation of hardware architectures and software strategies for LLM serving through features like a precomputed kernel library and trace-driven analysis.

- Chapter 5: Chiplet Cloud: A TCO-Optimized LLM Hardware Architecture proposes Chiplet Cloud, a cloud-scale, chiplet-based ASIC architecture [145].

This work focuses on the economic viability of large-scale LLM deployment and is optimized for the Total Cost of Ownership (TCO) of LLM inference. Key aspects include fitting model parameters within on-chip memory, co-optimizing chip size with software mapping, and exploiting model sparsity.

- Chapter 6: ChronoStack: A 3D-Memory Architecture for Long-Context LLMs describes ChronoStack, a 3D memory architecture developed as part of a collaborative research effort to which the author contributed, designed to tackle the memory bandwidth challenges posed by increasing context lengths in LLMs. It features a Time-Multiplexed KV-Prefetching technique, aiming to leverage the high bandwidth of hybrid-bonded 3D DRAM to accelerate attention operations and improve end-to-end latency in long-context LLMs.

- Chapter 7: Conclusion summarizes the key findings of this dissertation, reiterates the main contributions of the research, and discusses potential directions for future work in the field of AI hardware.

Collectively, the research detailed in these chapters offers an investigation into architectures and methodologies for AI inference hardware, covering aspects from foundational network acceleration to the specific requirements of contemporary large-scale language model serving.

Bibliographies: The work of Section 3.1 on iFPNA was published at [25] and [26]. The work of Chapter 4 ReaLLM simulator will be published at [146], and opensource at https://github.com/bespoke-silicon-group/reallm. The work of Chapter 5 Chiplet Cloud was published at [145].

#### Chapter 2

#### **BACKGROUND**

#### 2.1 Fundamentals of Early Models

In the landscape of artificial intelligence, early progress was profoundly influenced by foundational models such as Convolutional Neural Networks (CNNs), Recurrent Neural Networks (RNNs), and the emergence of Deep Reinforcement Learning (DRL) algorithms. This section presents a concise overview of the core architectures and methodologies that define CNNs, RNNs, and DRL.

#### 2.1.1 Convolutional Neural Networks and Recurrent Neural Networks

Convolutional Neural Networks (CNNs) are specialized neural networks designed to process grid-like data structures such as images. They leverage spatial locality by using convolutional layers, pooling layers, and fully connected layers. The convolution operation for a two-dimensional input g(x,y) with a two-dimensional filter f(i,j) is defined as:

$$(f * g)(x,y) = \sum_{i} \sum_{j} f(i,j) \cdot g(x-i,y-j)$$

(2.1)

This process extracts hierarchical feature maps that encode edges, textures, and complex patterns. Pooling layers reduce spatial resolution to improve computational efficiency and translation invariance. The fully connected layers map these high-level features to output classes. CNNs have dramatically advanced tasks like image classification, exemplified by networks such as AlexNet [106] and ResNet [71].

Recurrent Neural Networks (RNNs) are designed to handle sequential data, maintaining a hidden state that captures temporal dependencies. The basic RNN computation at time step t is:

$$h_{t} = \sigma(W_{xh}x_{t} + W_{hh}h_{t-1} + b_{h})$$

$$o_{t} = W_{ho}h_{t} + b_{o}$$

(2.2)

where  $\sigma$  is the non-linear function such as tanh,  $o_t$  is the output,  $h_t$  is the hidden state,  $x_t$  the current input, and  $W_{ho}$ ,  $b_o$ ,  $W_{xh}$ ,  $W_{hh}$ , and  $b_h$  are learnable parameters. Traditional RNNs often suffer from vanishing or exploding gradients; hence, LSTMs [73] and GRUs [36] were introduced, utilizing gating mechanisms to manage information flow effectively.

CNNs, RNNs, and their variants have distinct architectural patterns and computational characteristics. To effectively support the wide diversity of models and operations, the underlying hardware must be designed with versatility in mind. In Section 3.1, we present a flexible deep neural network accelerator architecture that can efficiently execute all these workloads.

#### 2.1.2 Deep Reinforcement Learning

Deep Reinforcement Learning (DRL) combines reinforcement learning with deep neural networks to allow agents to learn optimal policies from environment interactions. It is applied to applications that need to make real-time decisions continuously, such as video and board game playing, and robot motion control[171, 161].

One common reinforcement learning methodology is called Q-learning method. It learns a value function q(s,a), that estimates the expectation of the discounted return, or value, of an action in a certain state. Taking one of the most popular DRL algorithms, DQN [128], as an example. It uses deep neural networks to approximate the value function. It takes the environment states as inputs and outputs the value of each valid action. Unlike other DNNs, DRL generates datasets for training by interacting with the environment.

Similar to DNNs, DRL is also optimized to minimize the loss E between the network output and the target output  $\hat{O}$ ,

$$E = (q_{\theta}(S_i; A_i) - \hat{O})^2$$

(2.3)

where  $q_{\theta}$  is the value function (DNN) with parameter  $\theta$ , also called *online network*. The time step i is randomly sampled from the replay memory. The target output of DQN is

defined as,

$$\hat{O} = R_i + \gamma \max_{a'} q_{\bar{\theta}}(S_{i+1}; a') \tag{2.4}$$

The intuition of this function is the value q of a state  $S_i$  with an action  $A_i$  is equal to the immediate reward  $R_i$  plus the maximum q value of the next state  $S_{i+1}$ .  $\bar{\theta}$  represents the parameters of a target network. It is a periodic copy of the online network, and not directly optimized. This helps to reduce the correlation with the target value.

DQN has been widely used in later Q-learning algorithms, such as Rainbow [72], Ape-X [75], and R2D2 [94]. In Section 3.2, we design an accelerator that optimizes these Q-learning DRL algorithms.

#### 2.1.3 Neural Network Training

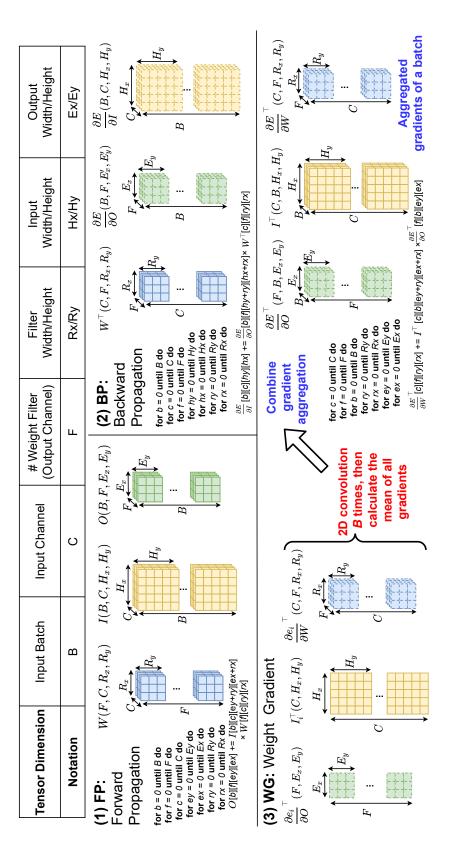

Neural network training adjusts model parameters to minimize a loss function through iterative optimization. The primary three phases are Forward Propagation (FP), Backward Propagation (BP), and Weight Gradient Computation (WG). In Figure 2.1, we illustrate the tensors and operations on a convolutional layer in these phases. Each phase has two input tensors and one output tensor, which are addressed using seven dimensions. B refers to the input batch, C refers to the input channel, F refers to the number of filters and the output channel. R, H, and E refer to the 2D spatial size of filter weight, input and output activation, respectively, with x, y are the 2D spatial coordinates. The color of the tensor indicates whether it is filter weight W (blue), input activation I (yellow) or output activation O (green). Gradient tensors are represented by the dashed lines, such as the output activation gradient  $\frac{\partial E}{\partial O}$  in BP.

During FP, a sliding-window 3D convolution is performed by filter weight W and input activation I to generate the output activation O. The detailed calculation process is shown in a 7-level nested loop, corresponding to 7 different dimensions across 3 tensors. The operation pattern in BP retains unchanged as what in FP. Note that the filter weight W are transposed at the C and F dimensions, and each plane of  $W_{R_x \times R_y}^{\top}$  is rotated 180 degrees.

Gradient aggregation embeds in gradient computation. Normally, the operations in WG phase are shown at the left side of Figure 2.1-(3). The weight gradients of the loss

on each sample in a batch, i.e.,  $\frac{\partial e_1}{\partial W}$ , ...,  $\frac{\partial e_N}{\partial W}$ , are computed first through a 2D convolution between the input activation and its corresponding output activation gradients. Then, the optimization function uses the mean values of all weight gradients to update the weight. The data movement for gradient aggregation becomes a performance bottleneck for DRL and many other DNNs training using data parallelism [119, 120, 116]. When we design accelerator for DRL in Section 3.2, we combine the weight gradient computation and aggregation in one phase. As shown in the right side of Figure 2.1-(3), the dimension B of  $\frac{\partial E}{\partial O}$  and I becomes the second axes of the tensor, which is accumulated during the computation. This combines the weight gradient computation and aggregation in one unified operation, thereby eliminating unnecessary data movement. Meanwhile, the operation pattern in WG is also unified with FP and BP as the same 7-level nested loop through this reshaping. Therefore, the dataflow introduced in Section 3.2 can be seamlessly applied to these three phases.

#### 2.2 Fundamentals of Large Language Models

#### 2.2.1 Decoder-Only Transformer Architecture

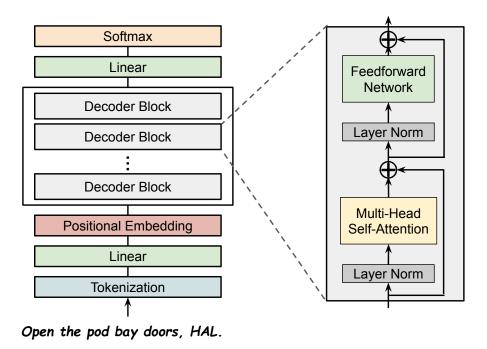

Large Language Models (LLMs) predominantly utilize the Transformer architecture, introduced by Vaswani et al. [200]. Specifically, decoder-only Transformers are employed for autoregressive tasks such as text generation. The architecture, as shown in Figure 2.2 comprises a stack of multiple identical decoder blocks, each containing a Multi-Head Self-Attention (MHSA) mechanism, a Feed-Forward Network (FFN), Residual Connections and Layer Normalization.

Each token in the prompt is first embedded into a vector space and combined with positional encodings to retain sequence information. The output of the final decoder block is projected onto the vocabulary space using a linear transformation followed by a softmax function to obtain probability distributions over the next token.

#### Multi-Head Self-Attention (MHSA)

The self-attention mechanism allows the model to weigh the importance of different tokens in the input sequence when encoding a particular token. For an input sequence represented

Figure 2.1: Tensors and operations in three phases of a convolutional layer are shown in the block diagram and loop nest, with a unified pattern.

Figure 2.2: The decoder-only transformer model architecture.

by matrix  $X \in \mathbb{R}^{n \times d}$ , where n is the sequence length and d is the model dimension, the self-attention is computed as:

Attention

$$(Q, K, V) = \operatorname{softmax}\left(\frac{QK^{\top}}{\sqrt{d_k}}\right)V$$

(2.5)

Here, the queries Q, keys K, and values V are linear projections of the input:

$$Q = XW^Q, \quad K = XW^K, \quad V = XW^V \tag{2.6}$$

where  $W^Q, W^K, W^V \in \mathbb{R}^{d \times d_k}$  are learnable weight matrices, and  $d_k$  is the dimension of the key vectors.

To capture different types of relationships and features, multiple self-attention mechanisms, known as *heads*, are run in parallel:

$$MHSA(X) = Concat(head_1, ..., head_h)W^O$$

(2.7)

where each head is computed as:

$$head_i = Attention(XW_i^Q, XW_i^K, XW_i^V)$$

(2.8)

and  $W^O \in \mathbb{R}^{hd_k \times d}$  is a learnable projection matrix.

To improve efficiency and scalability, several variants of the attention mechanism have been proposed:

- Multi-Query Attention (MQA): Uses a single set of keys and values for all heads, reducing memory usage and computational cost [167].

- Grouped-Query Attention (GQA): Groups multiple queries to share keys and values, balancing between MHA and MQA in terms of performance and efficiency [6]. Figure 2.3 shows the block diagram of a transformer block with GQA.

- Multi-head Latent Attention (MLA): Compresses key and value inputs into lower-dimensional latent vectors, which significantly reduces the Key-Value (KV) cache size for more efficient inference [46, 47].

These variants are particularly beneficial during the decoding phase of inference, where efficiency is critical.

Feed-Forward Network (FFN)

Each Transformer layer includes a FFN, which usually consists of two linear projections with a non-linear activation in between:

$$FFN(x) = \sigma(xW_1)W_2 \tag{2.9}$$

where  $\sigma$  is the non-linear activation such as ReLU,  $W_1 \in \mathbb{R}^{d \times d_{ff}}$ ,  $W_2 \in \mathbb{R}^{d_{ff} \times d}$ , and  $d_{ff}$  is typically larger than d, allowing the model to capture complex patterns [200].

Variants using Gated Linear Units (GLU) introduce a different structure [168]. An FFN with GLU, such as SwiGLU (using the Swish activation) or GEGLU (using GELU),

employs three linear projections to create a gating mechanism that can selectively control the information flow, often leading to improved performance and training dynamics:

$$FFN_{GLU}(x) = (\sigma(xW) \otimes xV)W_2 \tag{2.10}$$

where xV acts as the gate and is element-wise multiplied by the activated output of the first linear projection. Figure 2.3 shows the block diagram of a transformer block with SwiGLU.

#### Mixture-of-Experts

Mixture-of-Experts (MoE) models introduce sparsity by activating only a subset of expert networks for each input, allowing for larger models without a proportional increase in computational cost. The routing mechanism determines which experts are activated:

$$MoE(x) = \sum_{i=1}^{E} G_i(x) \cdot Expert_i(x)$$

(2.11)

where E is the total number of experts, Expert<sub>i</sub> is the *i*-th expert network, and  $G_i(x)$  is the gating function output, often implemented as a softmax over the experts [169].

#### 2.2.2 Phases of LLM Inference

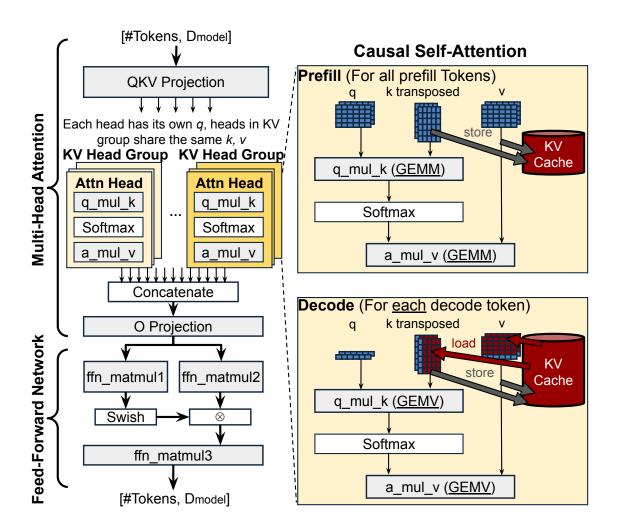

This inference process of generative LLM unfolds in two phases: prompt processing, or prefill, and token generation, or decode. The prefill stage occurs first and is used to generate only the first token of the response. All subsequent tokens are generated in the decode stage. This iterative process continues until a specific end-of-sequence (EOS) token is generated or the sequence reaches a predefined maximum length. The key operations of an attention head in prefill and decode are shown in the right part in Figure 2.3.

During the *prefill* stage, we compute over the full context of the input prompt to generate the first new token. This often turns the computation bounded as we have dense computation over the full input sequence. We also keep the key and value projections inside each layer of the self-attention block into a data structure called the *key-value* (KV) cache.

Figure 2.3: Key operations in a transformer block with grouped-query attention and SwiGLU activation function.

During the *decode* stage, only the last generated token is given as the input context. Inside the self-attention block, we need the KV projection for the entire context, thus the new token's KV projections are concatenated with the cached KV projection to attain the full context KV projection. This new token's KV projections are also written back to the cache for future tokens. Because the transformer decoder block is causal and masks backwards connections, the result using the KV cache is algebraically equivalent to recomputing the entire model on the full context.

The KV cache will significantly reduce the number of operations per token at the expense of maintaining the KV cache. It also makes the model significantly more memory bound. In the decode stage, as shown in lower right of Figure 2.3, each decode token has to do the self-attention independently. Therefore, two MatMul operations q\_mul\_k and a\_mul\_v become matrix-vector multiplications (GEMVs), which require a large KV cache load as the context length increases.

#### 2.3 System Techniques for AI Inference

#### 2.3.1 Multi-Device Parallelism

Large AI models such as LLMs require distributing operations across multiple devices (mapping) due to their computational and memory demands. This section covers five key multidevice parallelism paradigms. While Data Parallelism and Model Parallelism are broadly applicable to Deep Neural Networks (DNNs), Context Parallelism and Expert Parallelism are primarily employed in LLMs.

Data Parallelism (DP) [107, 117] replicates the entire model on each device, with each processing a subset of the input batch. DP is simple to implement but memory-intensive. It is commonly used in large batched DNN training to improve the training throughput, while the batch size of inference tasks can be very small, in which case data parallelism cannot take advantage of all nodes.

Model Parallelism [43] partitions the model itself, assigning parts to different devices. This reduces per-device memory but can increase inter-device communication. Depending on the partition dimension, there are Tensor Model Parallelism (TP) and Pipeline

Model Parallelism (PP) [78, 104, 213, 55]. TP partitions individual model layers across devices. Operations within layers are distributed, requiring frequent synchronization, such as partial sum accumulation and layer normalization. PP assigns blocks of layers to devices, and all devices operate in a pipelined fashion. Compared to TP, PP eliminates most of the inter-node communication.

Context Parallelism (CP) [118, 212] distributes the input sequence across multiple devices or processing units. Instead of processing an entire sequence on a single device, context parallelism divides the tokens so that different parts of the sequence are handled in parallel. CP helps reduce memory pressure and improves throughput, especially for long-context inputs, by enabling devices to work on separate portions of the sequence simultaneously while synchronizing only the necessary intermediate states.

**Expert Parallelism (EP)** [51], used in Mixture of Experts (MoE) models, distributes numerous specialized *expert* subnetworks across devices. EP scales model capacity while keeping per-token computation manageable, but faces challenges in load balancing and efficient token routing.

These parallelism strategies are often combined, and the choice of which to use, or how to combine them, is critical for achieving optimal performance and efficiency in large-scale AI inference.

#### 2.3.2 Dynamic Batching and Scheduling for LLM Serving

Efficiently serving LLMs requires sophisticated batching and scheduling techniques to maximize throughput and resource utilization while maintaining acceptable latency for users. Batching, the process of grouping multiple requests for simultaneous processing, is particularly critical for improving throughput, especially for inference tasks like token generation during decoding, which often have a low arithmetic intensity. However, naive batching strategies applied to interactive requests, such as those in chat applications, can introduce unacceptable end-to-end latency. Dynamic batching techniques aim to strike a balance between these competing objectives.

Several batching strategies have been developed to address different aspects of the latency-

throughput trade-off in LLM serving:

Standard Batching (or Static Batching) is the traditional approach where incoming requests are grouped into batches, often of a fixed size, before execution. A key drawback is potential underutilization: all requests in a batch are typically processed until the longest sequence completes, often involving padding shorter sequences. This means compute resources can be idle while waiting for the entire batch to finish, especially when sequence lengths vary significantly.

Continuous Batching (CB) [216] improves upon static batching by processing a dynamic batch of requests. In each iteration, the system processes all active requests in the current batch. New requests can be added to the batch as they arrive and capacity permits, and completed requests are removed. Consequently, new requests do not have to wait for all preceding requests in a fixed batch to finish. This significantly improves system utilization and reduces average latency, especially for dynamic workloads with varying request rates and lengths.

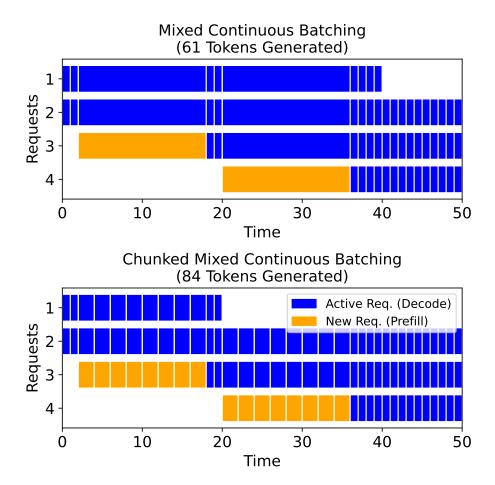

Mixed Continuous Batching (MCB) [74] further refines CB by enabling the prefill phase of new requests to be processed concurrently with the decode phase of ongoing requests within the same iteration, as illustrated in the top plot of Figure 2.4. This strategy efficiently interleaves the compute-intensive prefill operations with the memory-bandwidth-bound decode operations. MCB enhances hardware utilization and reduces queueing delays, proving particularly beneficial in interactive settings where responsiveness is key.

Chunked Mixed Continuous Batching (C-MCB) [4] addresses the challenge of large prefill requests, which can still significantly increase iteration times even in MCB. C-MCB mitigates this by dividing large prefill computations into smaller, more manageable chunks. This allows decode operations for active requests to be interleaved more finely with these prefill chunks, minimizing the latency impact of long prompts on other requests, as shown in the bottom plot of Figure 2.4. By carefully selecting chunk sizes, C-MCB can prioritize decode tasks, thereby improving overall system utilization and throughput. While chunking might imply additional KV-cache operations, this typically incurs negligible performance overhead because the prefill phase is generally compute-bound rather than memory-bound.

Figure 2.4: Comparison of mixed continuous batching (MCB) and chunked mixed continuous batching (C-MCB).

#### 2.3.3 Hardware-Aware Model Co-design

Beyond optimizing system-level scheduling and batching for existing models, a significant trend in improving AI inference efficiency involves hardware-aware model co-design. This paradigm no longer views AI models and hardware architectures as independent entities, but instead advocates a synergistic approach where model architectures, algorithms, and even training methodologies are developed with explicit consideration of the underlying hardware's capabilities and constraints [64]. This holistic strategy becomes increasingly important, especially for large-scale models like LLMs, where the interplay between model complexity and hardware limitations determines the overall performance, cost, and energy efficiency.

Recent large-scale LLM deployments provide compelling examples of this co-design concept. For example, the DeepSeek-V3 system demonstrates how hardware-aware model design choices can lead to more cost-efficient training and inference on existing GPU clusters [222]. Key aspects of such co-design include:

Memory Efficiency through Model Architecture: The enormous memory footprint of LLMs, particularly due to the Key-Value (KV) cache in Transformer attention mechanisms, is a primary target for co-design. Techniques like Multi-head Latent Attention (MLA), as employed in DeepSeek-V3, aim to reduce KV cache demands by compressing keyvalue representations, thereby improving memory efficiency and allowing for longer context lengths or larger batch sizes on memory-constrained hardware [47, 222]. Other model-side innovations like Grouped-Query Attention (GQA) [6] and Multi-Query Attention (MQA) [167] also represent efforts to make attention mechanisms more hardware-friendly from a memory perspective.

Computational and Communication Co-optimization: For models incorporating techniques like Mixture of Experts (MoE), which scale model capacity by selectively activating sub-networks (experts), co-design is crucial. The routing of tokens to experts and the communication patterns for aggregating expert outputs must be optimized in conjunction with the hardware's interconnect topology and parallelism capabilities. DeepSeek-V3 [222] discusses optimizing their MoE architecture for the specific NVIDIA H800 GPU cluster, con-

sidering computation-communication trade-offs and employing techniques like node-limited routing.

Leveraging Low-Precision Arithmetic: Modern AI hardware often includes specialized units for lower-precision arithmetic (e.g., FP8, INT8) to improve throughput and reduce memory bandwidth. Hardware-aware model co-design involves training or fine-tuning models to be robust to these lower precisions (e.g., through quantization-aware training or specific training recipes for formats like FP8). This ensures the model can effectively utilize the hardware's peak performance capabilities without significant accuracy degradation.

Hardware-Aware Neural Architecture Search (NAS): Another dimension of codesign involves incorporating hardware performance metrics (e.g., latency, energy) directly into the search process for optimal neural network architectures [49]. This ensures that the discovered architectures are not only accurate but also efficient on the target hardware platform.

The insights from such large-scale deployments and research efforts highlight that achieving optimal efficiency for demanding AI workloads, particularly LLMs, increasingly requires a departure from a siloed approach to model and hardware development. Instead, a deeply integrated co-design process, where algorithmic innovations evolve in tandem with architectural features, is becoming the norm to push the frontiers of AI system performance and scalability.

## 2.4 Specialized Hardware Acceleration

The computational demands of state-of-the-art AI models, especially Large Language Models (LLMs), have exceed the capabilities of general-purpose processors like CPUs and GPUs. This has created an urgent need for specialized hardware accelerators to deliver the required performance and energy efficiency.

# 2.4.1 Motivation for ASICs

General-purpose CPUs are designed for a wide range of tasks and offer great flexibility, but their architecture is not inherently optimized for the highly parallel, matrix-multiplyintensive operations that dominate AI computations. While GPUs, originally designed for parallel graphics rendering, have been successfully repurposed for AI workloads due to their massively parallel architecture, they still retain some general-purpose overheads and may not always provide the optimal balance of performance, power, and cost for specific AI tasks at scale.

Application-Specific Integrated Circuits (ASICs) offer a solution by providing hardware tailored to the computational patterns of AI algorithms [87, 27, 41]. By designing circuits from the ground up for tasks like convolution, matrix multiplication, and activation functions, ASICs can achieve the following:

**Higher Performance:** Dedicated data paths and massive parallelism allow ASICs to perform AI computations significantly faster than general-purpose hardware.

Greater Energy Efficiency: By eliminating unnecessary general-purpose logic and optimizing data movement, ASICs consume less power for the same AI workload, a critical factor for both edge devices and large-scale datacenter deployments.

Lower Cost at Scale: While the initial design cost (Non-Recurring Engineering, or NRE) of ASICs is high, for high-volume applications, the per-unit manufacturing cost can be lower than that of complex general-purpose chips, leading to better Total Cost of Ownership (TCO).

The rise of LLMs, with their enormous parameter counts and computational needs, has further intensified the drive towards AI ASICs. The sheer scale of computation required to train and serve these models makes efficiency paramount, and ASICs provide a pathway to achieve this at the scale demanded by modern AI applications.

# 2.4.2 Principles of Hardware Acceleration for AI

Effective hardware acceleration of AI depends on several key architectural principles and optimization techniques:

Specialized Compute Units: Instead of general-purpose ALUs, AI accelerators feature dedicated units for operations like MAC (Multiply-Accumulate), vector processing, and sometimes specific activation functions. Tensor cores with systolic arrays, which perform matrix-matrix multiplications efficiently, are a prime example [109, 87, 132].

**Dataflow Architectures:** The way data (activations, weights, partial sums) is moved and processed within the accelerator is critical. Different dataflow strategies (e.g., weight stationary, output stationary, input stationary, row stationary as discussed in Section 3.1 or more flexible schemes like F|B|C as discussed in Chapter 3.2 for DRLP) aim to maximize data reuse and minimize energy-intensive data movement to and from off-chip memory. Systolic arrays are a common architectural pattern that implements specific dataflows efficiently [28, 29, 112].

Memory System Optimization: Traditionally, this involves memory hierarchies with large on-chip SRAM (caches, scratchpads, buffers) to keep frequently accessed data (weights, activations, LLM KV cache) near compute units, reducing costly off-chip data movement (e.g., DRAM or HBM) [87, 29]. Emerging paradigms further minimize data transfer. Near-memory processing moves compute closer to memory (e.g., in 3D stacks). In-memory computing or processing-in-memory (PIM) performs computations directly within memory arrays (e.g., using ReRAM or specialized SRAM/DRAM) [5, 166, 165].

Reduced Precision and Quantization: Many DNNs can tolerate computations at lower numerical precision (e.g., 16-bit floating point (FP16/BF16), 8-bit integers (INT8), or even lower) with minimal loss in accuracy. Using reduced precision reduces memory footprint, memory bandwidth requirements, and the energy/area of compute units [68, 86].

Sparsity Exploitation: DNN weights and activations can often be sparse (containing many zero values). Hardware that can skip computations involving zeros or store sparse data in compressed formats can significantly improve performance and efficiency [68].

The effectiveness of AI accelerators is evaluated based on several metrics:

- Throughput: Operations per second (e.g., TOPS, FLOPS) or inferences or tokens per second.

- Latency: Time taken to complete a single inference or generate a token.

- Energy Efficiency: Operations throughput normalized by power (e.g., TOPS/W), or energy per operation (e.g., Joule/Inference, Joule/Token).

- Area Efficiency: Operations per unit of silicon area (e.g., TOPS/mm<sup>2</sup>).

- Total Cost of Ownership (TCO): Includes capital expenditure (chip cost, server cost) and operational expenditure (power, cooling) over the system's lifetime. For cloud providers and large-scale deployments, TCO per unit of performance (e.g., TCO/Token) is often the ultimate metric.

# 2.4.3 Challenges in AI Accelerator Design

Despite the potential benefits, designing efficient and effective AI accelerators presents numerous challenges [176, 157].

The Memory Wall: As compute capabilities increase, providing sufficient memory bandwidth and capacity to keep the PEs fed with data becomes a primary bottleneck. This is particularly acute for memory-bound operations common in LLMs, such as the attention mechanism and large embedding table lookups.

Scalability: AI models continue to grow in size and complexity. Designing architectures that can scale efficiently to accommodate future models, both within a single chip and across multiple chips/servers, is a major hurdle. This involves scalable interconnects, memory systems, and programming models.

Flexibility vs. Efficiency Trade-off: Highly specialized ASICs can achieve peak efficiency for a specific model or task but may perform poorly on others. As AI algorithms rapidly evolve, designing accelerators that offer a good balance between efficiency and programmability/flexibility to support a range of current and future models is crucial.

Power Delivery and Thermal Management: High-performance accelerators can consume significant power, leading to challenges in power delivery networks and heat dissipation, especially in dense server environments or power-constrained edge devices.

Hardware-Software Co-design: Achieving optimal performance requires close interaction between hardware architecture and software (compilers, runtime systems, mapping strategies). Compilers must efficiently map complex AI models onto the parallel hardware, optimizing data movement and resource utilization [40].

Cost and Non-Recurring Engineering (NRE): The design and verification of an

ASIC involve substantial upfront NRE costs, including expenses for design tools, engineering effort, and silicon mask sets. For an ASIC to be economically viable, these NRE costs must be amortized over a sufficiently large volume of chips or justified by significant TCO savings compared to alternative solutions [98, 123].

# 2.4.4 The NRE Challenge and Amortization in the Era of LLMs

The high NRE costs associated with ASIC development have traditionally been a barrier to their widespread adoption, especially for applications with uncertain market sizes or rapidly changing algorithms. However, the landscape is shifting with the advent of large-scale AI deployments, particularly for LLMs.

The immense demand for LLM inference capabilities, driven by applications like chatbots, content generation, and AI-powered search, translates into a massive volume of computations. As discussed in [145], the operational TCO of running these workloads on existing general-purpose hardware (like GPUs) at the required scale can be extraordinarily high. For instance, serving applications like ChatGPT or integrating LLMs into high-volume web search implies a TCO that can run into hundreds of millions or even billions of dollars annually. In such high-demand scenarios, the substantial TCO savings offered by an efficient, specialized ASIC can quickly outweigh its initial NRE. Even if an ASIC offers only a modest percentage improvement in TCO/Token compared to GPUs, the sheer volume of tokens generated means that the cumulative TCO savings can amortize the NRE relatively quickly.

Figure 2.5 shows the minimum required TCO/Token improvement in order to justify the NRE. We extend the NRE model from Moonwalk [98] to use a 7nm technology node and estimate the NRE of an ASIC accelerator for large language models to be approximately \$35M, including silicon mask cost, CAD tools, IP licensing, flip-chip BGA packing, server designs, and labor. Even if it were \$100M, the current cost of running workloads like ChatGPT and web search with integrated LLMs is so massive that it not only justifies the cost of creating ASIC supercomputers but going even further as to co-optimize those supercomputers for specifics LLMs for additional improvement in TCO per token.

Therefore, while NRE remains a significant factor, the unprecedented scale of LLM de-

Figure 2.5: Minimum TCO/Token improvement required from an ASIC to justify NRE costs as a function of baseline TCO on existing hardware.

ployment is creating a scenario where the economic benefits of specialized ASICs can overcome this initial investment, paving the way for more customized and efficient AI hardware.

# Chapter 3

# FOUNDATIONAL WORK: ACCELERATING EARLY AI PARADIGMS

The rapid evolution of artificial intelligence has been characterized by increasingly complex neural network models. Before the recent dominance of Large Language Models (LLMs), significant research focused on developing efficient hardware for earlier paradigms like Convolutional Neural Networks (CNNs), Recurrent Neural Networks (RNNs), and Deep Reinforcement Learning (DRL). These foundational models, while significantly smaller in scale than modern LLMs, presented their own unique challenges for hardware designers, including diverse computational patterns, memory access bottlenecks, and the need for flexibility. This chapter details foundational research undertaken during the author's doctoral studies, exploring architectures designed to accelerate these earlier AI workloads. These explorations provided critical insights and experience that informed the subsequent focus on LLM acceleration. Specifically, we will discuss iFPNA, a flexible processor targeting diverse early models, and DRLP, a specialized accelerator tackling the unique demands of Deep Q-Learning, including its emulation on cloud FPGAs.

## 3.1 iFPNA: A Flexible and Efficient Deep Learning Processor in 28nm CMOS

The discussion, figures, and tables related to the iFPNA architecture presented in this section are based on and reprinted from our prior work published in [26].

As deep learning algorithms evolved rapidly, the need for hardware that could adapt to various network types (CNNs, RNNs, Fully Connected networks) became apparent. Fixed data flow schemes in early processors limited their coverage of different algorithms, motivating the development of more flexible solutions.

The instruction and Fabric Programmable Neuron Array (iFPNA) architecture was developed collaboratively to address this need [26]. Presented as a 28nm CMOS chip prototype, iFPNA aimed to accelerate a variety of DNNs efficiently on a single platform. The iFPNA

Figure 3.1: The iFPNA architecture.

architecture combines instruction-level programmability as in an Instruction Set Architecture (ISA) with logic-level reconfigurability as in a Field-Programmable Gate Array (FPGA) in a sliced structure for scalability. Four data flow models, namely weight stationary, input stationary, row stationary and tunnel stationary, are described as the abstraction of various DNN data and computational dependence. The iFPNA compiler partitions a large-size DNN to smaller networks, each being mapped to, optimized and code generated for, the underlying iFPNA processor using one or a mixture of the four data-flow models. Experimental results have shown that various CNNs, RNNs, and FC networks can be mapped to the iFPNA processor, achieving the near ASIC performance.

## Architecture Overview